| Technical Name | Standard cell library synthesis for FinFET technology nodes | ||

|---|---|---|---|

| Project Operator | National Chiao Tung University | ||

| Project Host | 李毅郎 | ||

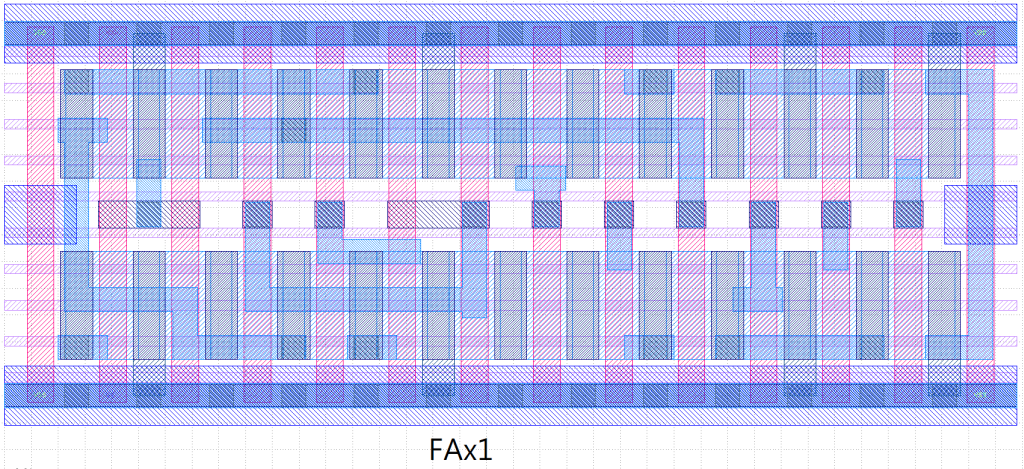

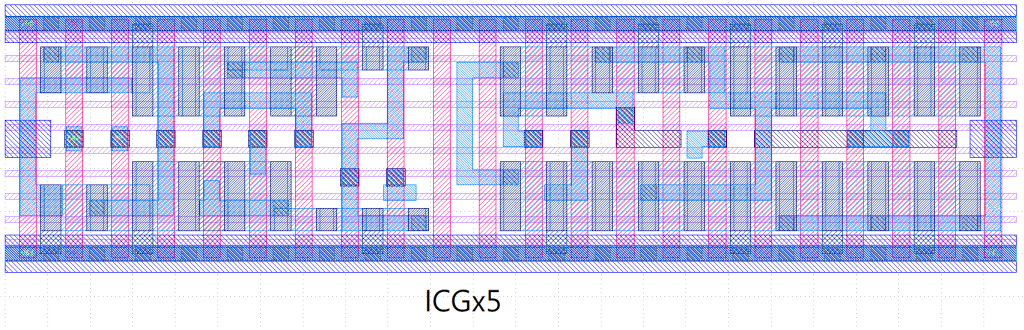

| Summary | The standard cell library synthesis that has been researched over 30 years never achieves the goal of producing higher quality of cell library than that of manual cell library. We propose a cell library synthesis flow with several innovative ways. The tests on the ARM ASAP 7nm implies we are the first team to achieve the goal of making better cell layouts than the manual ones in all aspects. |

||

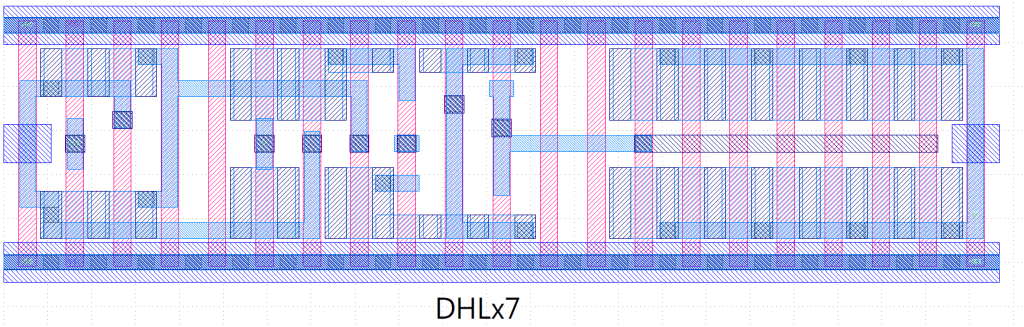

| Scientific Breakthrough | Our new ways are: Gradually set the optimal locations of diffusion contacts during routing; concurrently complete the IO pin placement and cell routing; minimize the M0 usage to complete all cell layouts; distribute the rule checking into different routing phases such that new rules can be handled. We are the first team to synthesize cells whose quality are little better than the manual design. |

||

| Industrial Applicability | Cell library synthesis can help foundry to fast obtain the performance and cost estimation and various simulations. For IC design service and IC design companies, cell libraries are their important IPs and can contribute to differentiating their products. We have well synthesized several cell libraries (more than 1000 cells) at two different process nodes at three cell heights (7.5, 9 and 12T). |

||

| Keyword | Standard cell library synthesis FinFET transistor cell layout synthesis transistor placement cell routing design rule manufacturing rule automatic rule violation repair cell layout optimization cell height | ||

- ylli@cs.nctu.edu.tw

other people also saw