| 技術名稱 | 前瞻異質半導體元件整合之單晶片三維堆疊超高密度邏輯閘(20M NAND-Gate/mm^2)積體電路技術 | ||

|---|---|---|---|

| 計畫單位 | 國立臺灣大學 | ||

| 計畫主持人 | 劉柏村 | ||

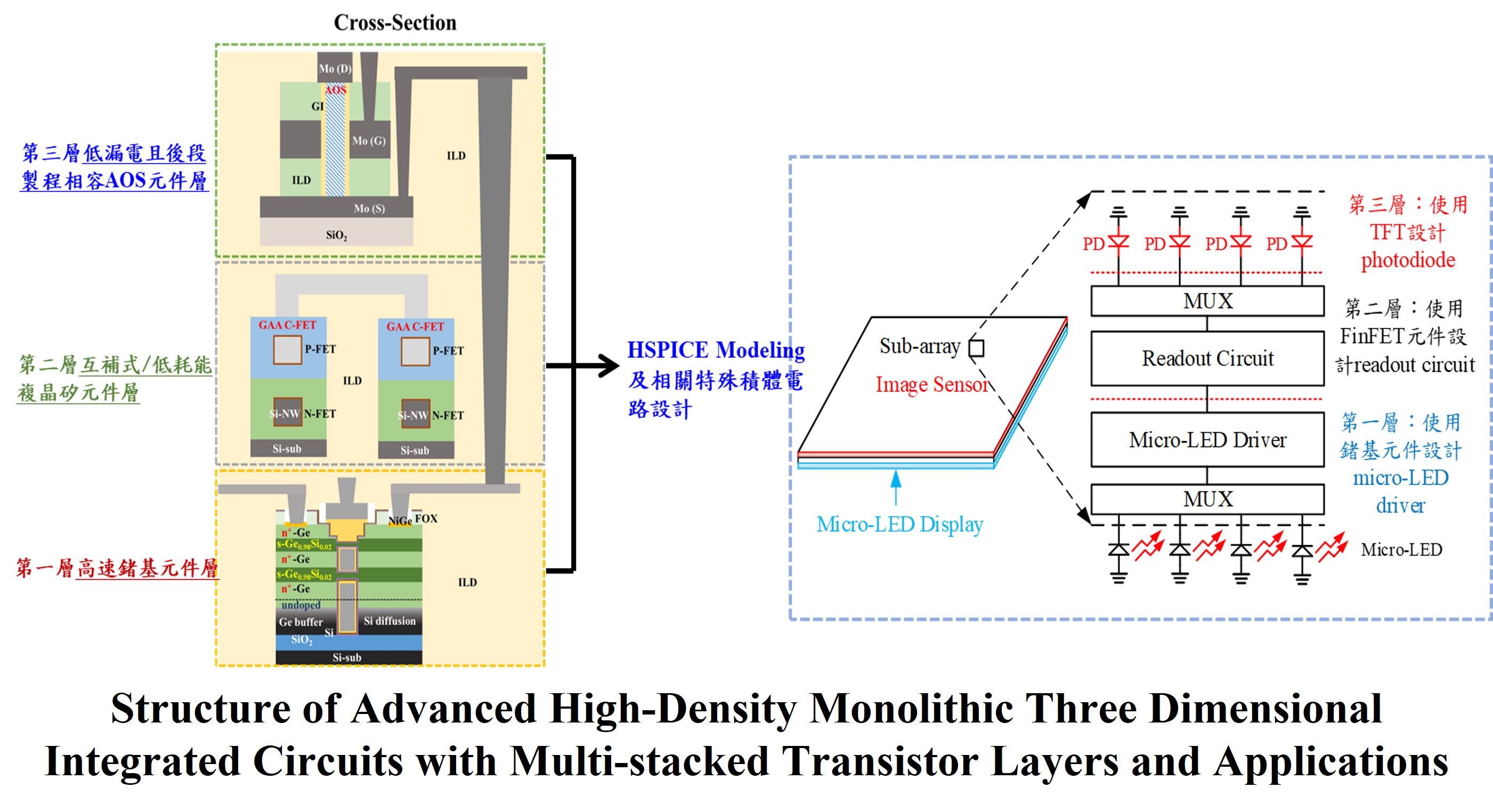

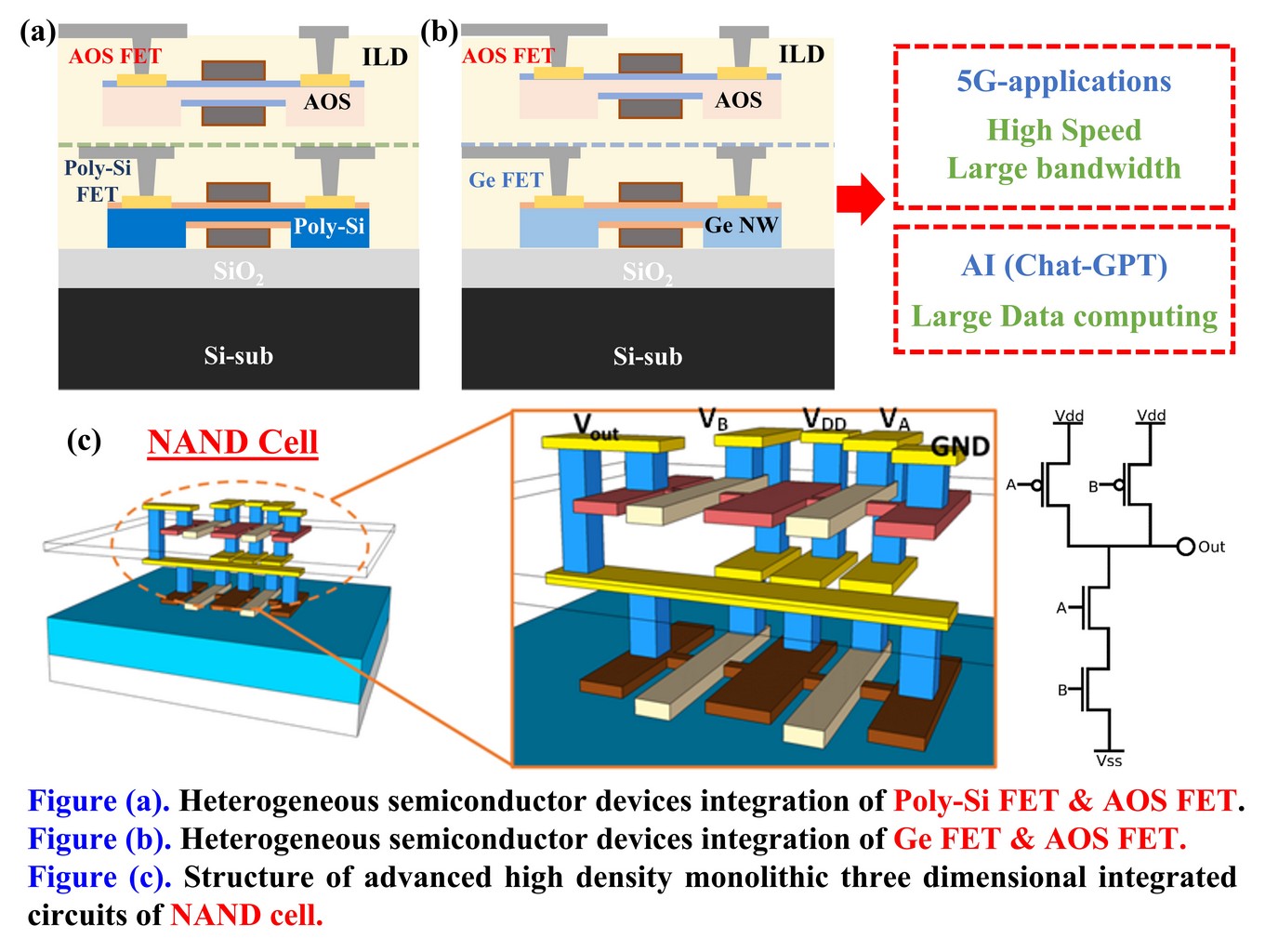

| 技術簡介 | 開發應用於超高密度邏輯閘之前瞻單晶片三維異質半導體整合積體電路技術,技術亮點為高效能異質半導體元件研發與整合,目前已達成階段性成果亮點,同時,也規劃發展多層級堆疊元件層之佈局與層間金屬連線整合技術,最終以達成世界級紀錄的三維堆疊式超高密度反及閘電路(20M NAND-Gate/mm^2)之目標。 |

||

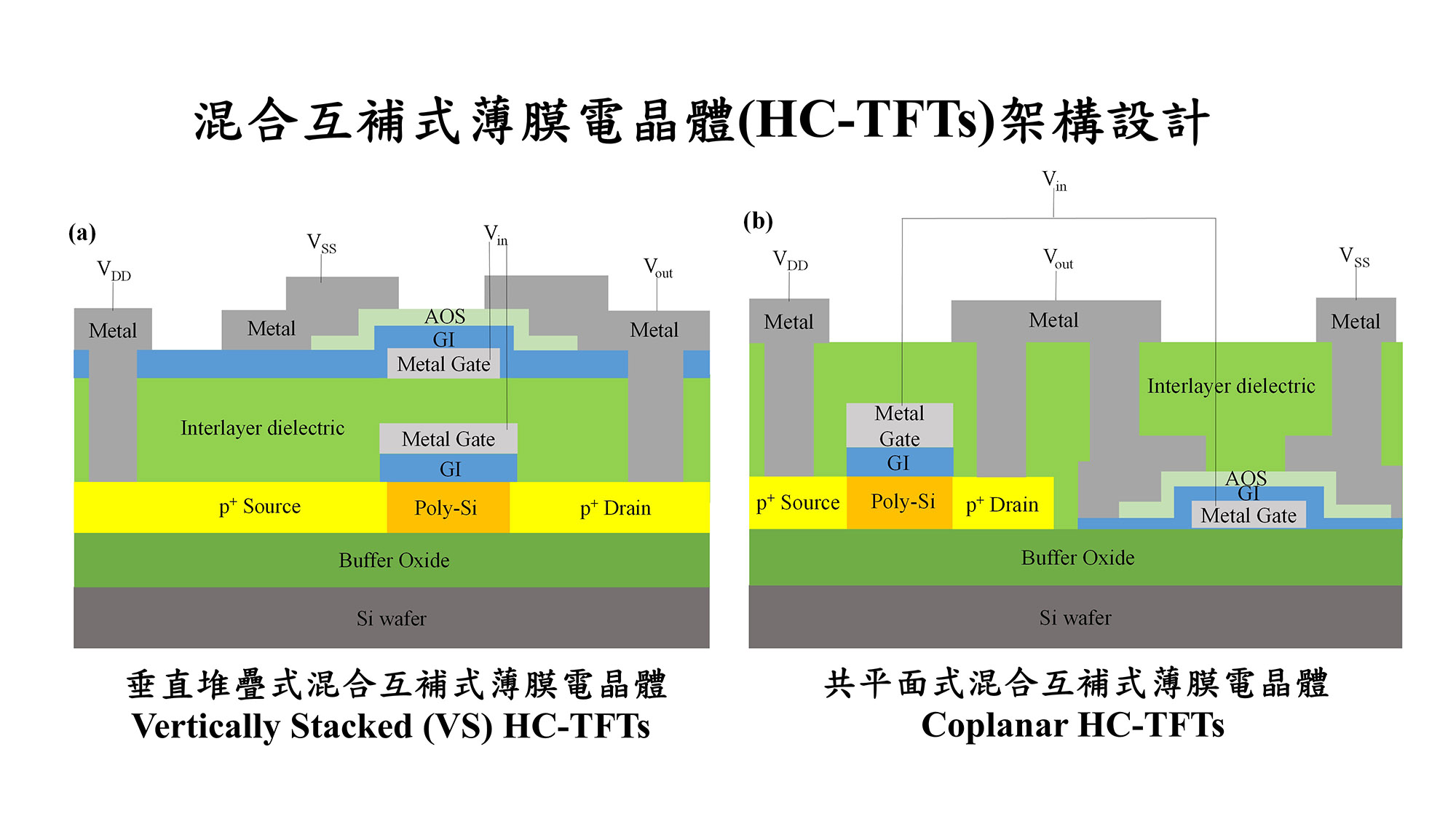

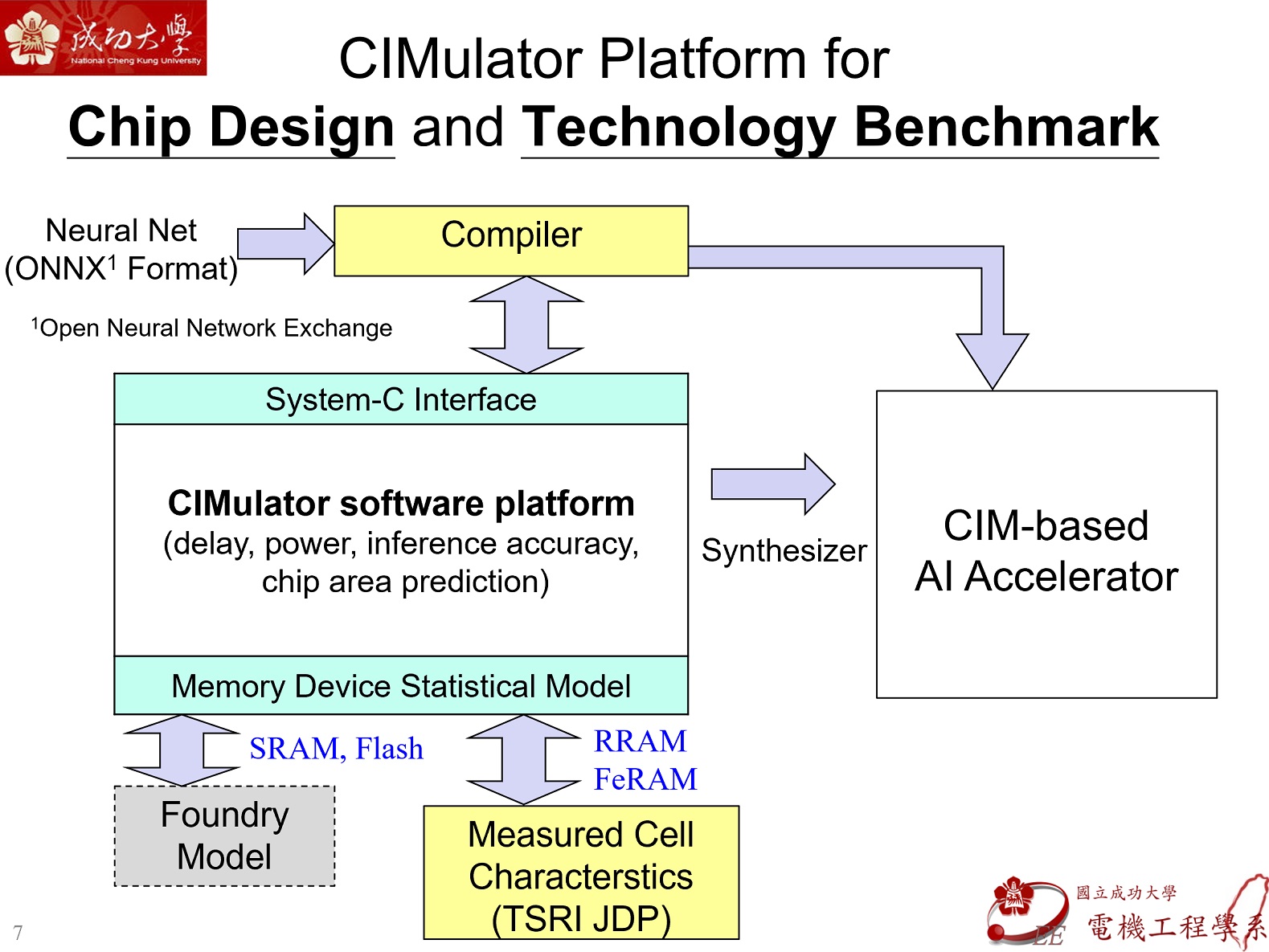

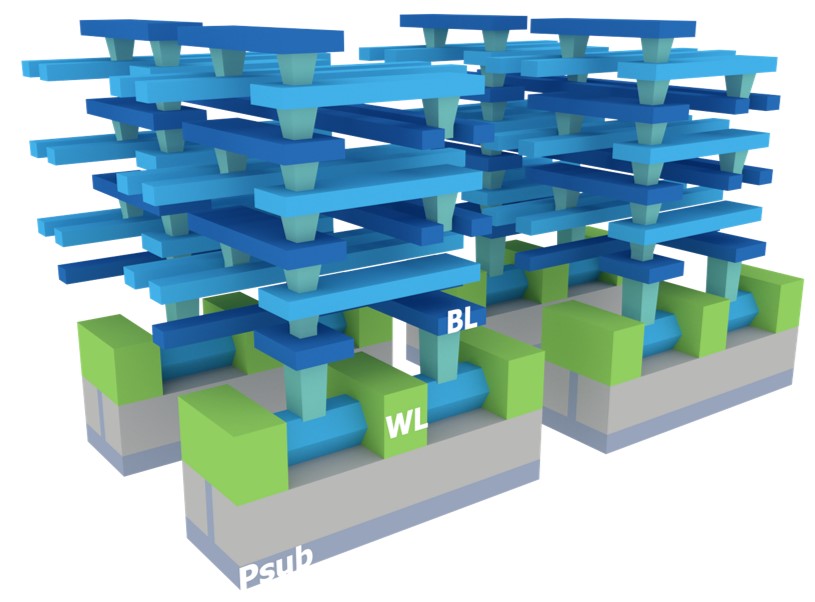

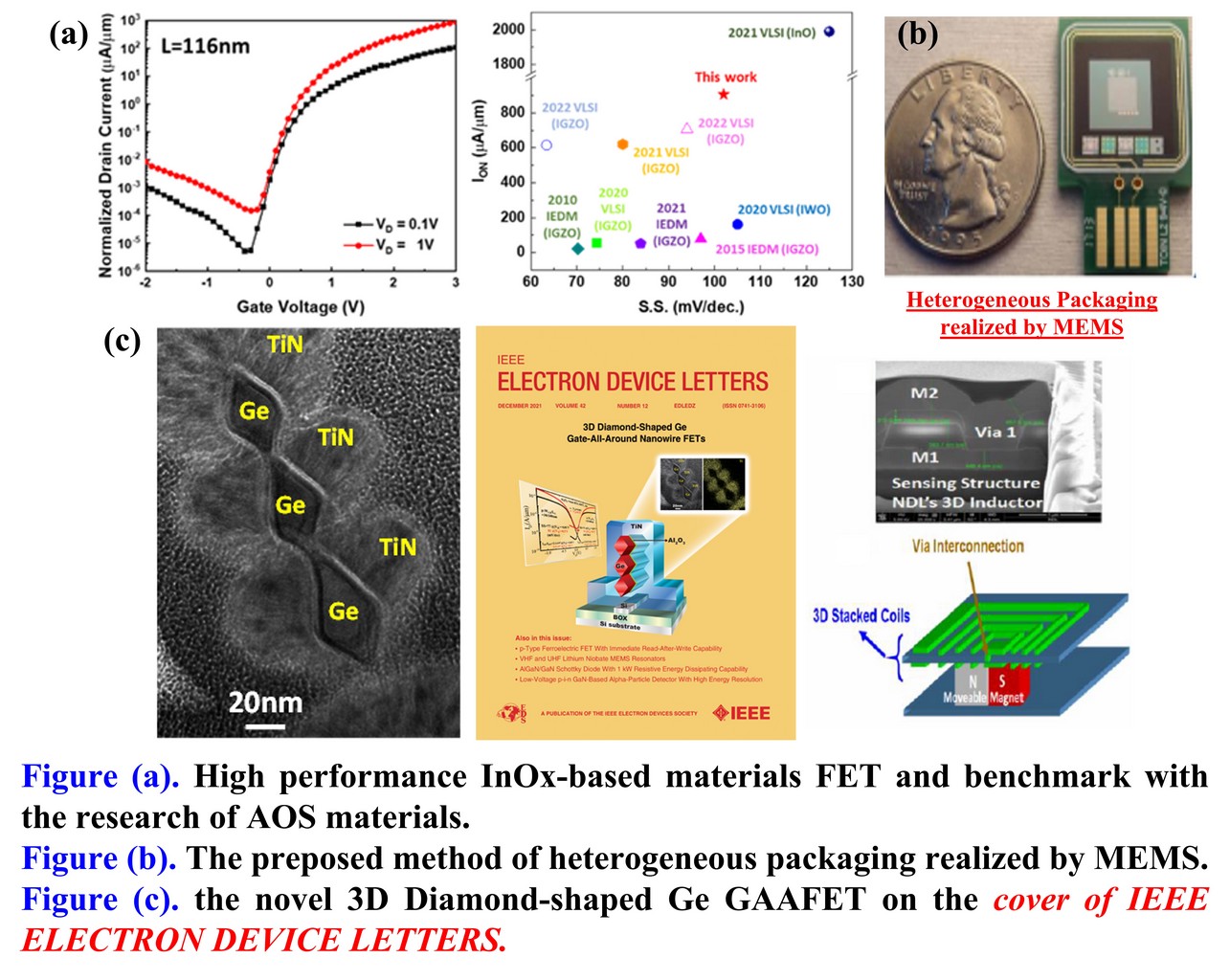

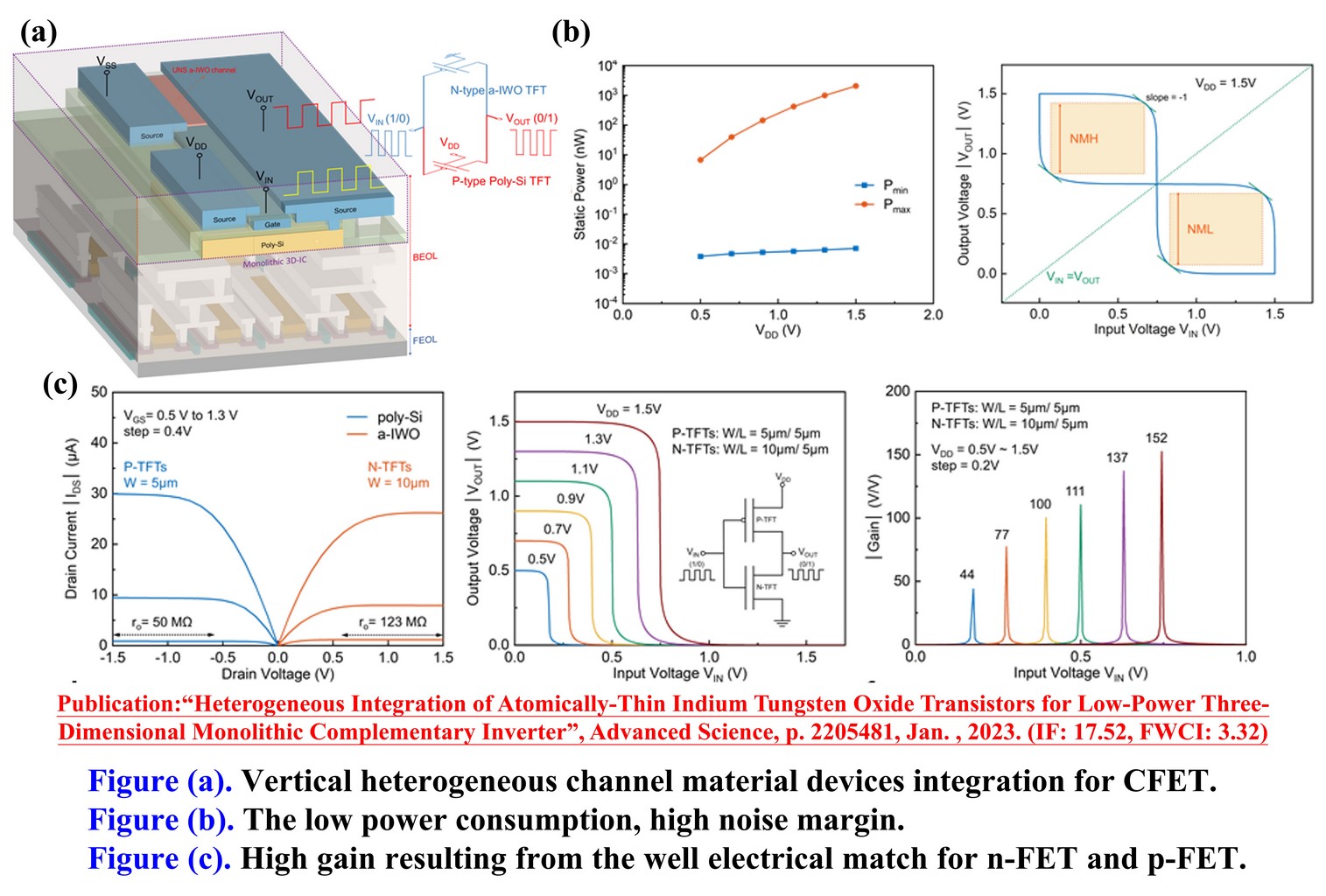

| 科學突破性 | 本團隊開發前瞻異質半導體元件整合之單晶片三維超高密度邏輯閘積體電路技術,閘極環繞式鍺基通道電晶體、低溫複晶矽元件與高效能氧化銦基薄膜電晶體技術已完成開發,最終將以達成世界級紀錄的超高密度20M NAND-Gate/mm^2實現為目標,本技術創新具有未來科學的突破性,亦為引領半導體技術發展的重要指標。 |

||

| 產業應用性 | 本團隊已開發高遷移率鍺基閘極環繞式電晶體、複晶矽電晶體與氧化銦基薄膜電晶體,並將此異質半導體元件整合成三維高密度積體電路,形成20M NAND/mm^2的邏輯電路,等效電晶體密度高達80 M/mm^2,提供了埃米級半導體積體元件/電路技術平台,極具潛力應用於前瞻電子、電信網路通訊與人工智慧產業。 |

||

| 關鍵字 | 閘極環繞式場效電晶體 非晶氧化物半導體 閘極環繞式氧化銦基薄膜電晶體 低溫複晶矽 高遷移率通道材料 奈米片環繞式閘極電晶體 鍺基材料 三維元件 異質整合 反及閘 | ||

- 聯絡人

- 蔣宗哲

- 電子信箱

- tcchiang.ee08@nycu.edu.tw

其他人也看了