| 技術名稱 | 可應用於單晶片三維積體電路與超高解析度顯示背板之異質互補式薄膜電晶體元件技術 | ||

|---|---|---|---|

| 計畫單位 | 國立交通大學光電工程系 | ||

| 計畫主持人 | 劉柏村 | ||

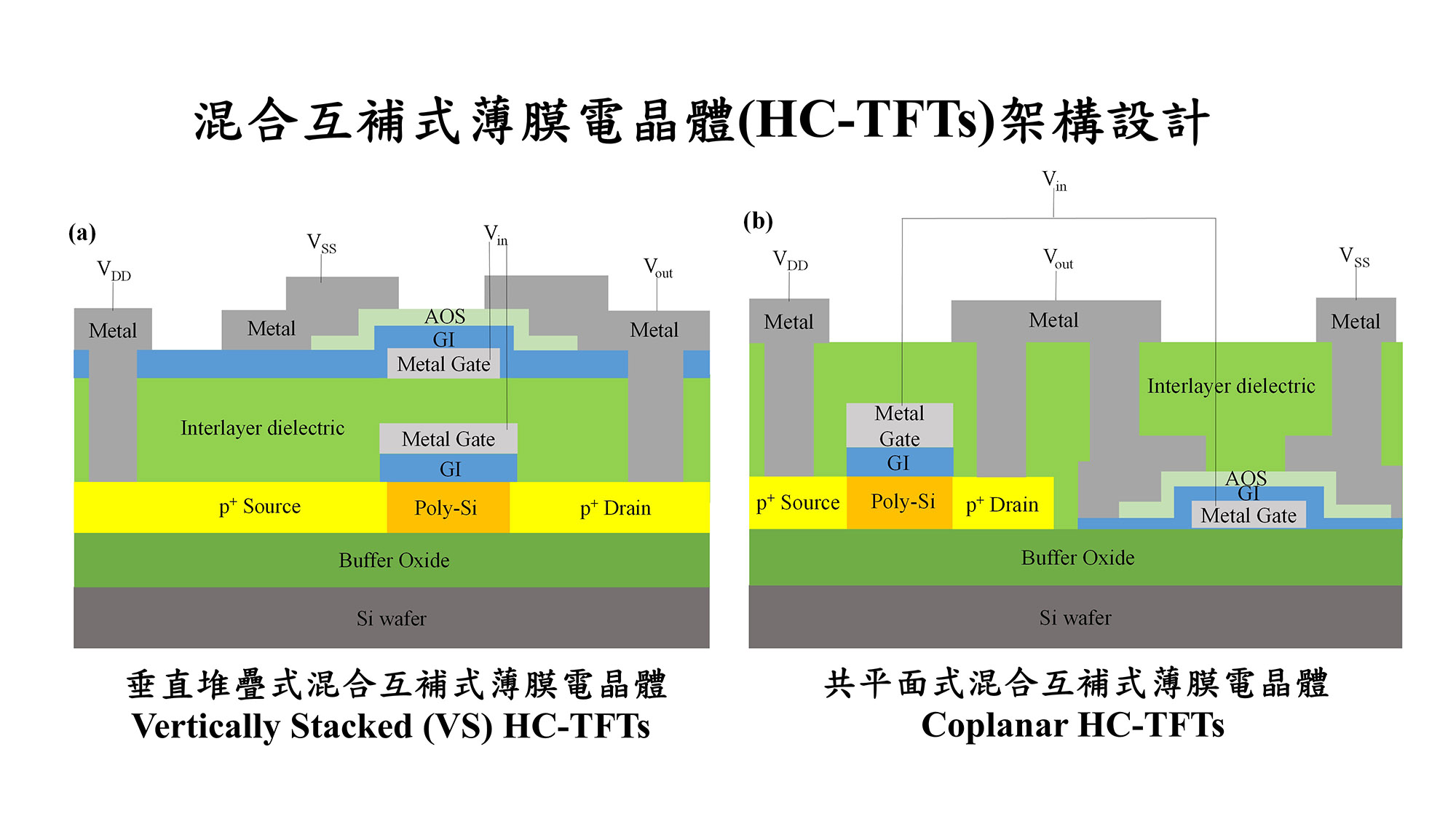

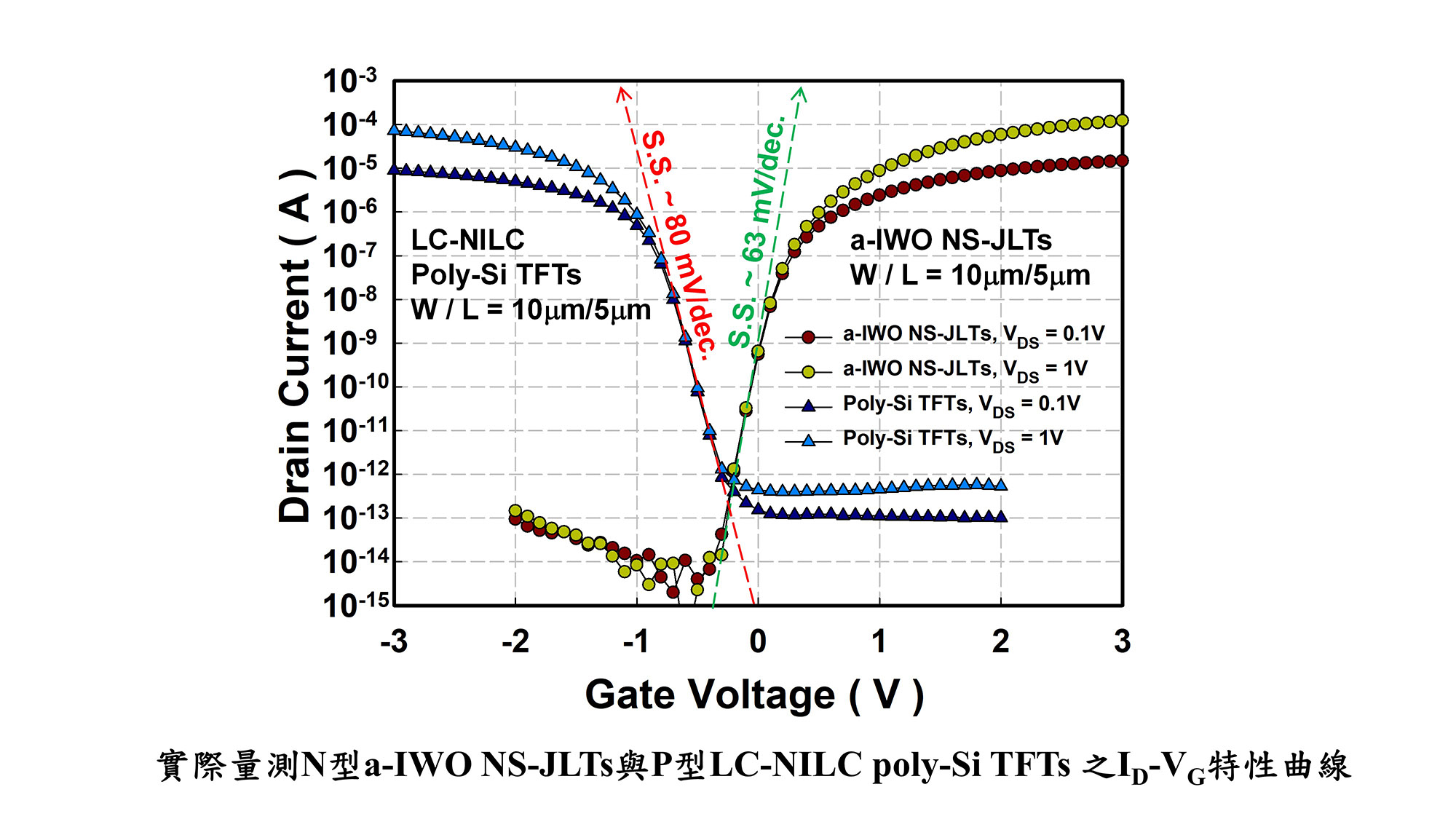

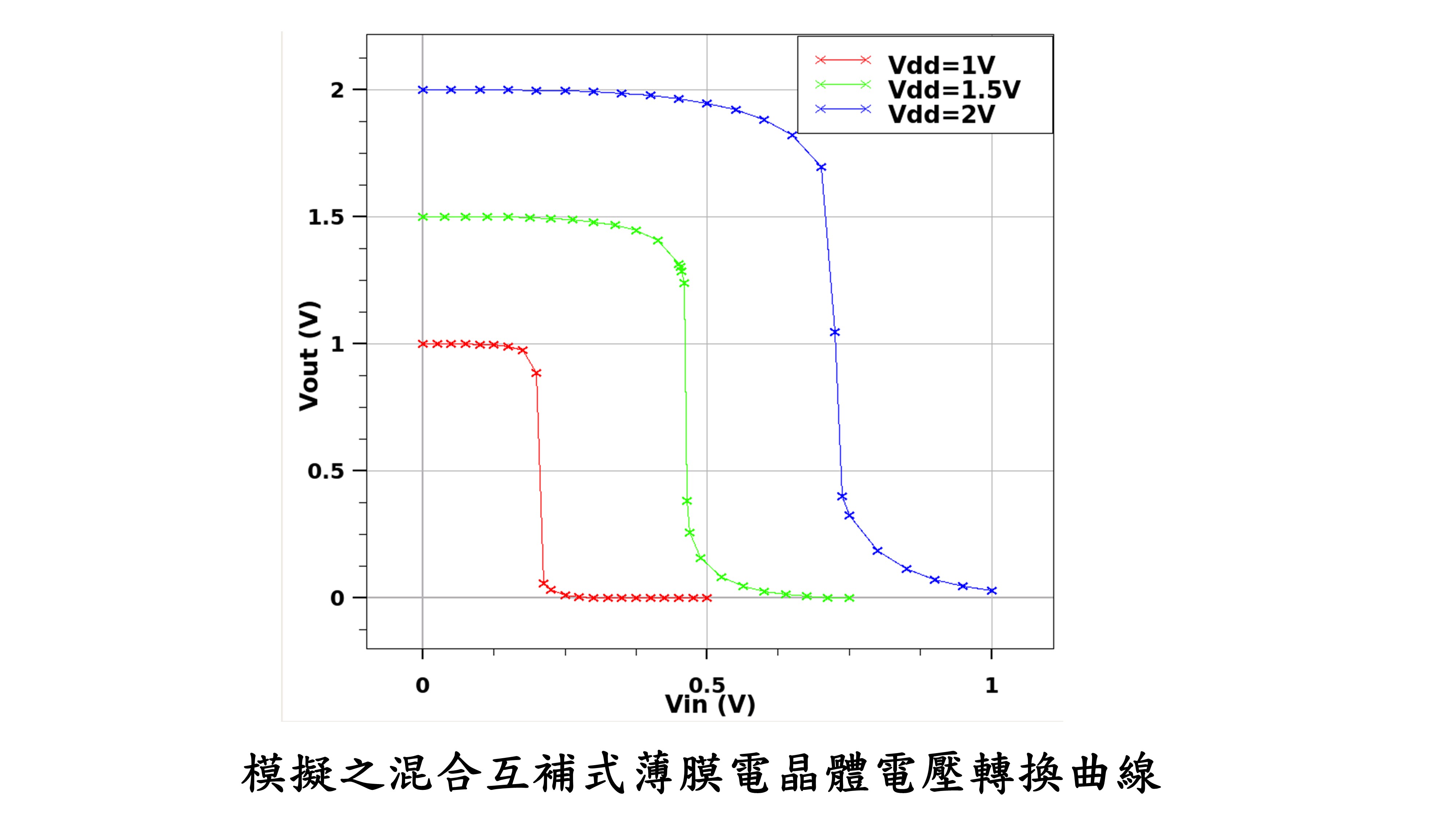

| 技術簡介 | 人工智能AI與5G等技術崛起,使得電晶體元件尺寸必須依循摩爾定律(Moore’s law)持續縮小,以增加IC運算速率與效能。然而,隨著元件微縮到物理極限,單晶片三維積體電路整合技術(Monolithic 3D-IC)的發展便受到相當大的矚目。單晶片3D-IC技術是在第一層電晶體元件/電路完成後,將第二層電晶體元件/電路製作並堆疊於第一層電路上方,以達到增加元件積集度、降低功率耗損與整合多功能電路為目標。然而,第二層電晶體電路製作的技術,受到許多的限制與挑戰,包括:製程溫度 (<400˚C)、製程相容性、平坦度和均勻性等。本專題計畫成果的技術突破處,乃是在於發展低製程熱預算置備的N型非晶氧化半導體和高效能P型複晶矽薄膜組成的異質互補式薄膜電晶體電路架構(Hybrid Complementary Thin-Film Transistors, HC-TFTs),並應用此高效能與低功耗的互補式元件於單晶片3D-IC技術中。本計畫所研發的前瞻HC-TFTs技術具有以下特色: 材料新穎性、元件尺寸匹配性、電路設計簡易、低元件漏電流、高載子遷移率、低功耗,以及與金屬連線製程的高度相容性。在N型薄膜元件技術的研發中,本研究已成功利用非晶氧化銦鎢(a-IWO)奈米薄片(4nm),發展出兼具低操作偏壓與高效能薄膜電晶體元件,奈米薄片結構可阻斷電晶體元件中源極與汲極之間的漏電路徑,降低尺寸縮小的短通道效應。在P型複晶矽薄膜電晶體技術中,我們也成功利用新穎非對稱性低汙染鎳側向誘發結晶技術(Low-contamination nickel induced lateral crystallization, LC-NILC)製作出低漏電流的P-型複晶矽薄膜電晶體元件。LC-NILC技術是利用鎳沉積於非晶矽表面,和矽反應生成金屬矽化物,加熱驅使鎳擴散到矽內部,由於鎳的晶格常數和矽相近,鎳的擴散會造成矽結晶,來降低複晶矽的結晶溫度,另外,我們在降低複晶矽薄膜中鎳金屬汙染物的含量,提高薄膜元件的特性以及操作可靠度。透過P型以及N型電晶體的電性量測資料,藉由元件參數萃取以及電腦輔助半導體技術模擬軟體的輔助(Technology Computer Aided Design, TCAD)建立混合互補式電晶體的物理模型,預測反相器與電路的最佳化特性與功效,可為未來前瞻3D-IC技術建立關鍵的技術發展平台。 |

||

| 科學突破性 | 本研究已成功整合N型無接面氧化銦鎢奈米薄片電晶體與非對稱式鎳側向誘發結晶P型複晶矽薄膜電晶體,均具低操作偏壓(≤ 2V)與其他優越元件特性,如: 近理想的次臨界擺幅~ 63mV/dec.與極低的漏電流,並研製出元件尺寸匹配的異質混合互補式反相器電路,可為前瞻三維積體電路技術的發展建立扎實的技術平台。 |

||

| 產業應用性 | 本計畫成果已成功開發出兼具高效能、低功耗的混合互補式邏輯反相器電路技術,實現於物聯網與人工智慧等多項前瞻電子產品中。此外,亦可將其應用於平面顯示技術,使顯示電路的設計富有彈性,提升顯示產品功能的多樣性與附加價值,舉凡電子標籤、車用中控台顯示、智慧型手機、醫療用顯示儀器等皆可應用其建構完整的驅動電路。 |

||

| 關鍵字 | 非晶氧化物半導體 低溫複晶矽 鎳側向誘發結晶 互補式金屬氧化物半導體 混合互補式薄膜電晶體 反向器 系統面板 電腦輔助半導體技術與元件模擬設計 單晶片三維積體電路 | ||

- 聯絡人

- 劉柏村

- 電子信箱

- ptliu@mail.nctu.edu.tw

其他人也看了