| Technical Name | 搭載畫素內嵌記憶體之低溫複晶矽氧化物薄膜電晶體陣列技術於超高解析度節能近眼穿戴顯示裝置應用 | ||

|---|---|---|---|

| Project Operator | Department of Photonics, National Chiao Tung University | ||

| Project Host | 劉柏村 | ||

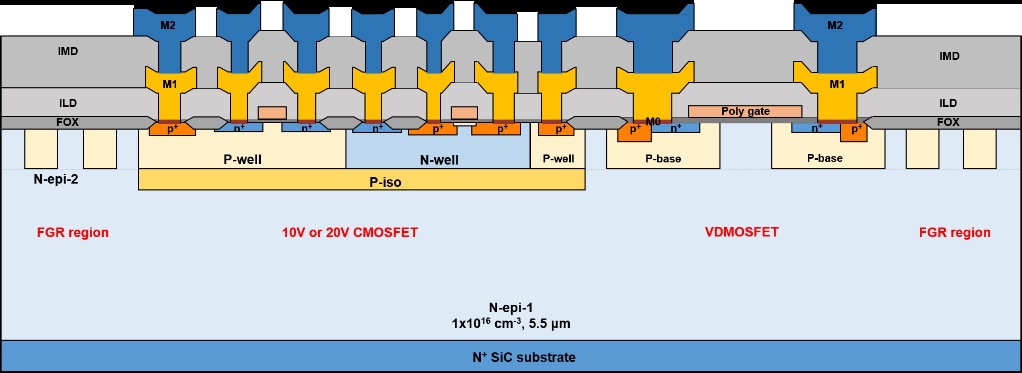

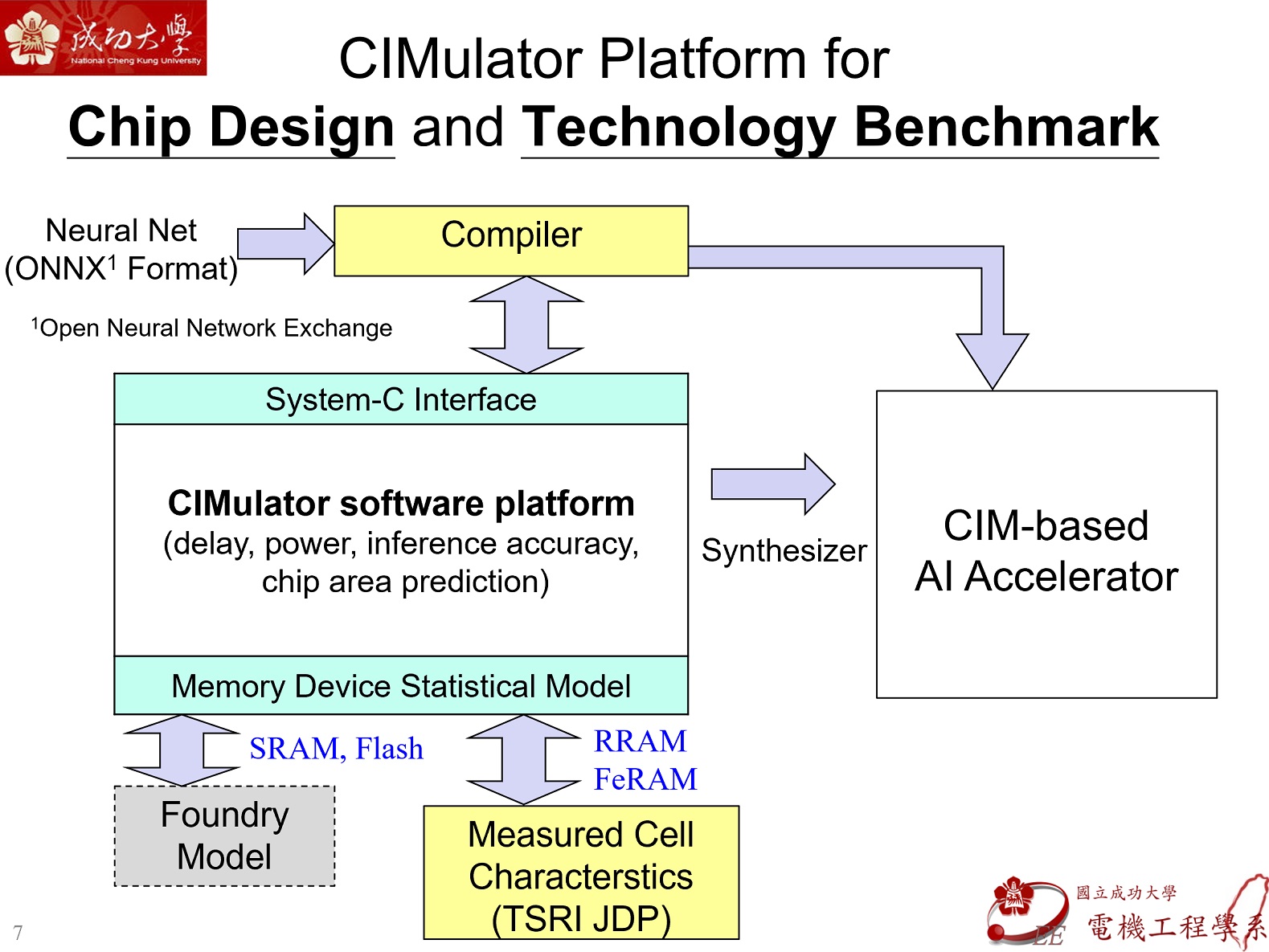

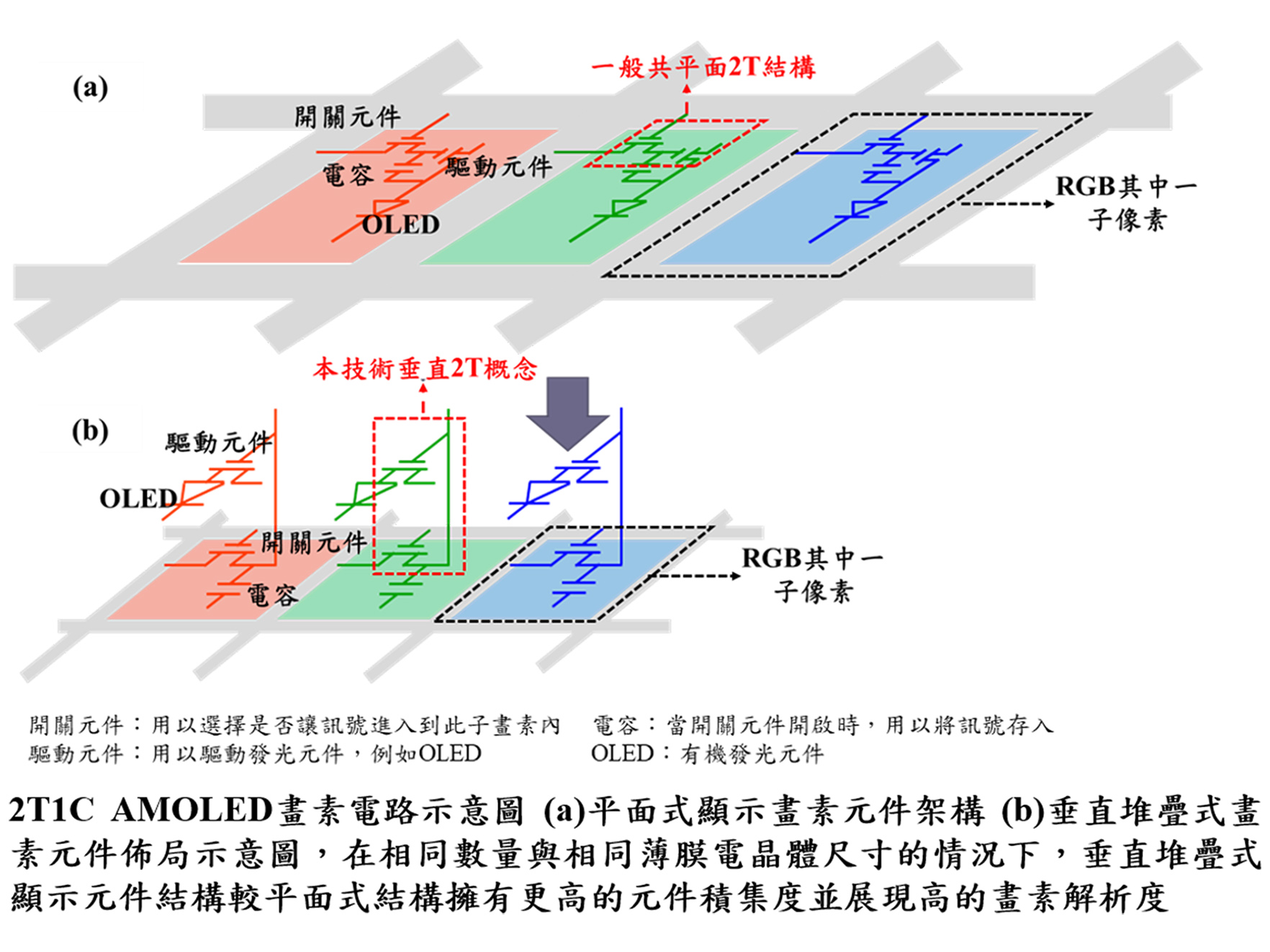

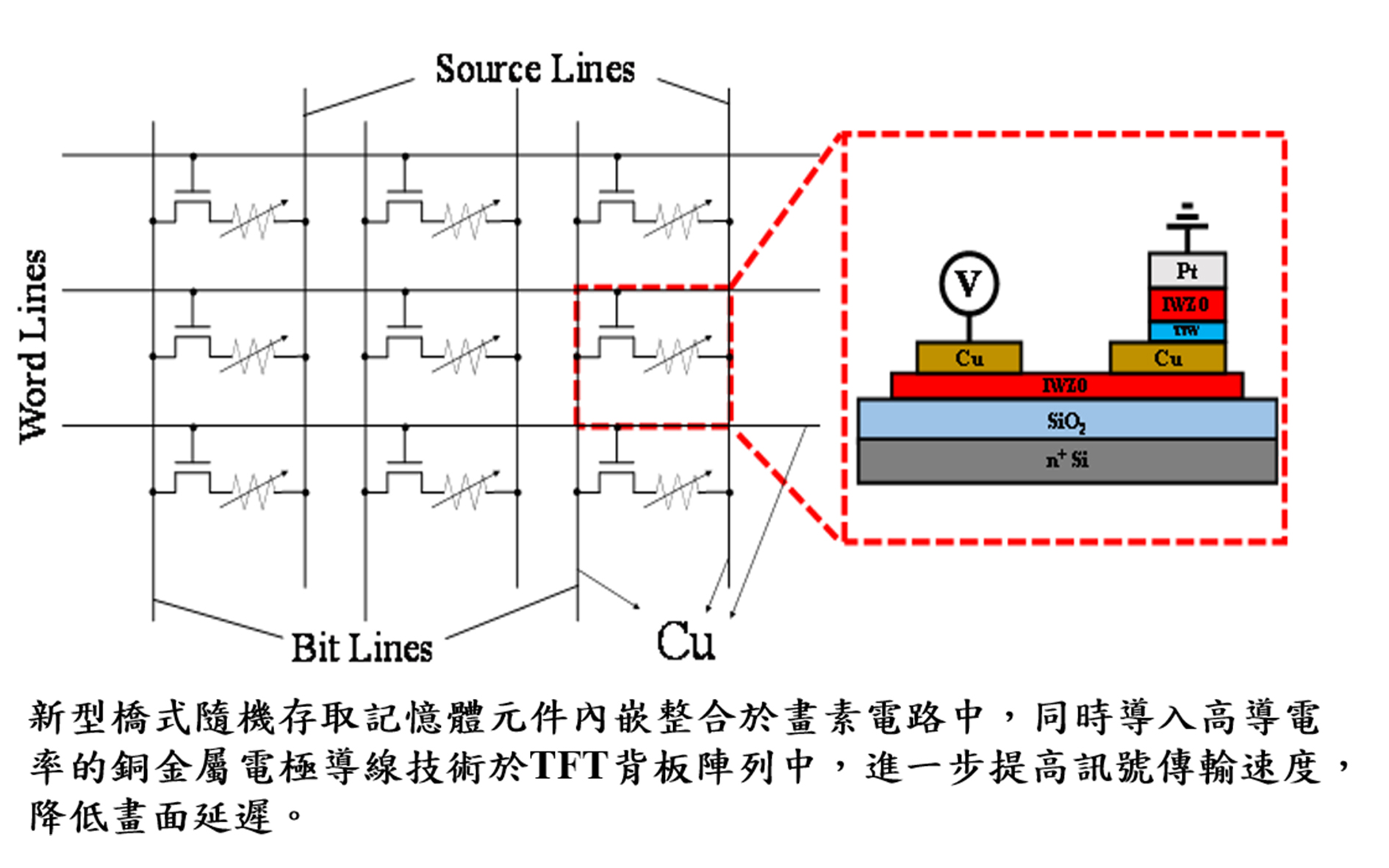

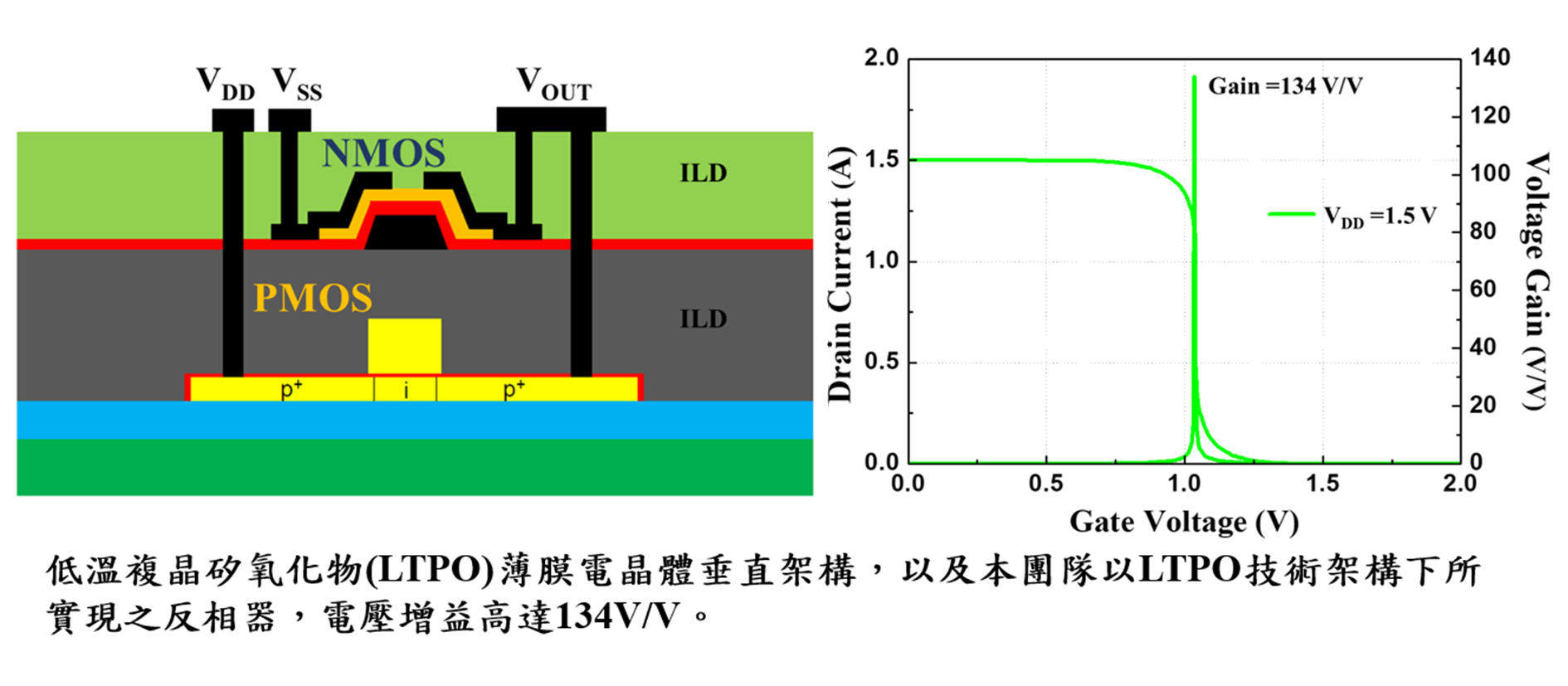

| Summary | A novel 3D-stack LTPO-based display array technology with CBRAM-embedded in a pixel has been successfully developed for the high-resolutionpower-saving near-eye VR/AR displays. Besides, a high-voltage gain CMOS inverter comprised by LTPO architecture is demonstrated acting as a digital driving circuit for the realistic FPD applications. |

||

| Scientific Breakthrough | In our work, a breakthrough in the bottleneck of N-channel AOS TFT performance has been made so that the novel 3D-stack LTPO architecture with nonvolatile CBRAM-embedded in pixel can be pioneerly developed acting as the display switch/driving array, applicable for the next-generation high-resolution near-eye VR/AR displays. The technology features low operation voltage, less device footprint in a pixel, low signal propagation delaylow power consumption, which are demonstrated by a high-voltage gain LTPO-based inverter. |

||

| Industrial Applicability | The displays with ultra-high resolutionlow-power consumption is highly demanded for the development trend of FPD industries. We have successfully proposed a high-performance vertical LTPO-based display array technologydemonstrated a high-voltage gain inverter. With the additional integration of CBRAM in pixel to store image signal, the frame rate can be effectively lowered, resultantly decreasing power consumption. It is highly promising to meet the FPD industry’s needs for the next-generation high-resolutionpower-saving VR/AR display electronics applications. |

||

| Matching Needs | 天使投資人、策略合作夥伴 |

||

| Keyword | Amorphous oxide semiconductor (AOS) Ultra nanosheet Junction-less Transistor (UNS-J Low-temperature polycrystalline silicon (LTPS) Low-temperature polycrystalline Oxide TFT (LTPO Inverter Conductive-bridging RAM (CBRAM) Memory in Pixel (MIP) Virtual reality/ Augment Reality (VR/AR) Ultra-high resolution Low Power Consumption | ||

- tcchiang.ee08@nycu.edu.tw

other people also saw