| 技術名稱 | 石墨烯在電子互連線應用的可行性技術 | ||

|---|---|---|---|

| 計畫單位 | 長庚大學 | ||

| 計畫主持人 | 陳始明 | ||

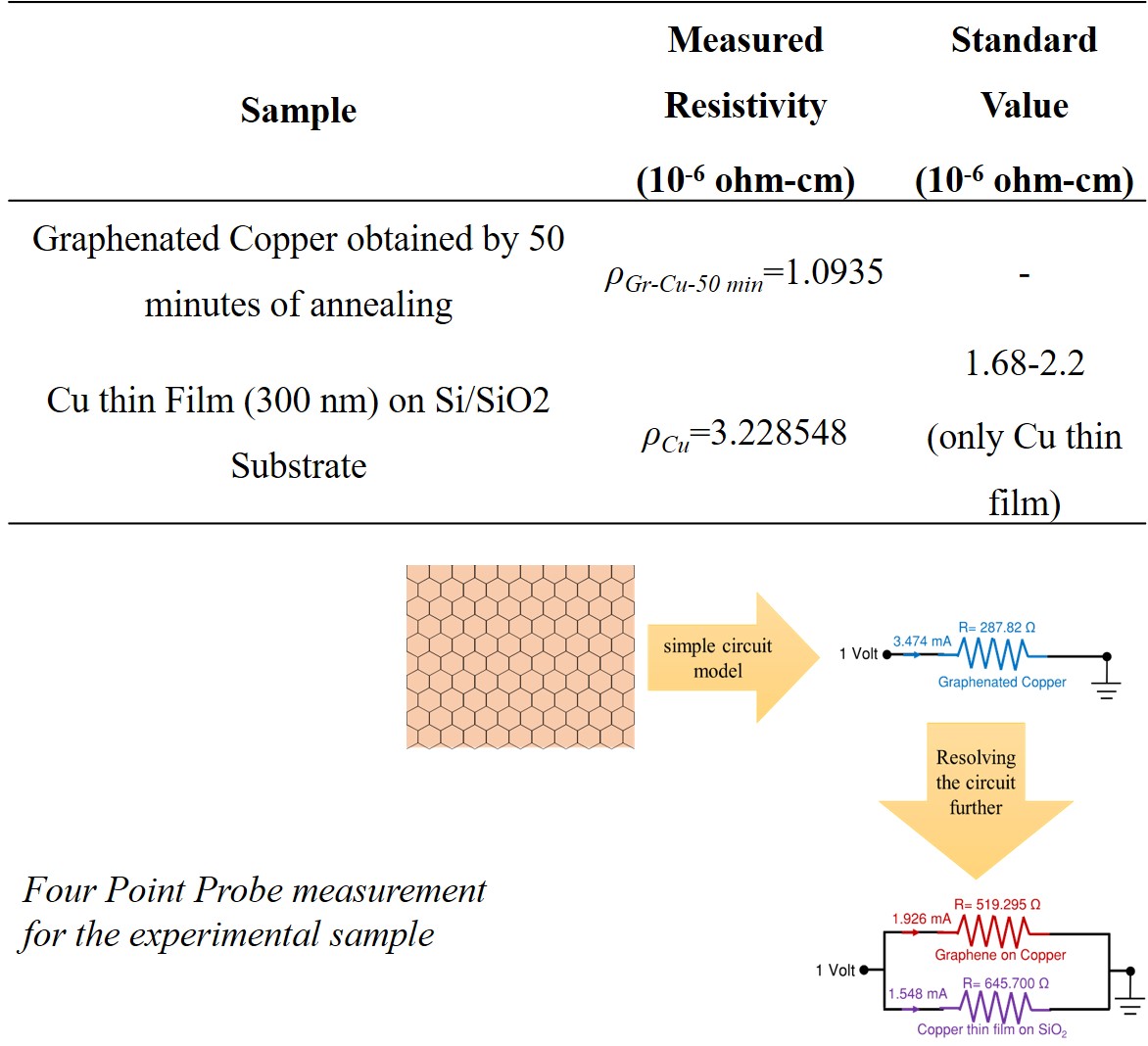

| 技術簡介 | 集成電路互連線目前正面臨進步的瓶頸。即使是銅互連,互連線引起的信號延遲比由晶體管所引起的延遲大兩到三個數量等級。分析還表明,當銅線的線寬從30 nm縮放到10 nm時,每單位長度的電阻增加了10倍以上。同樣的在較小的線寬下,導線必須承受較高的電流密度才能傳遞相同的電流,縮短導線的電遷移壽命,引起可靠度問題。 |

||

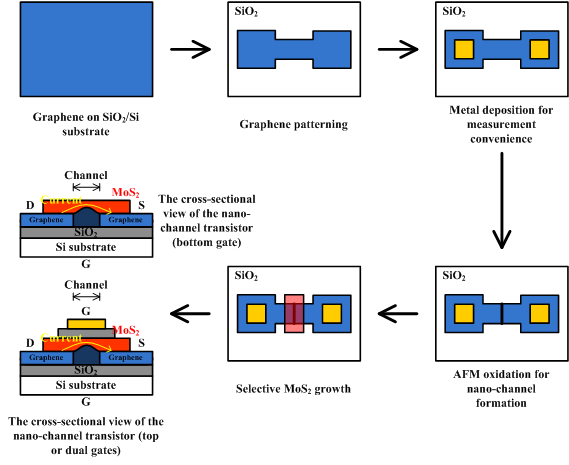

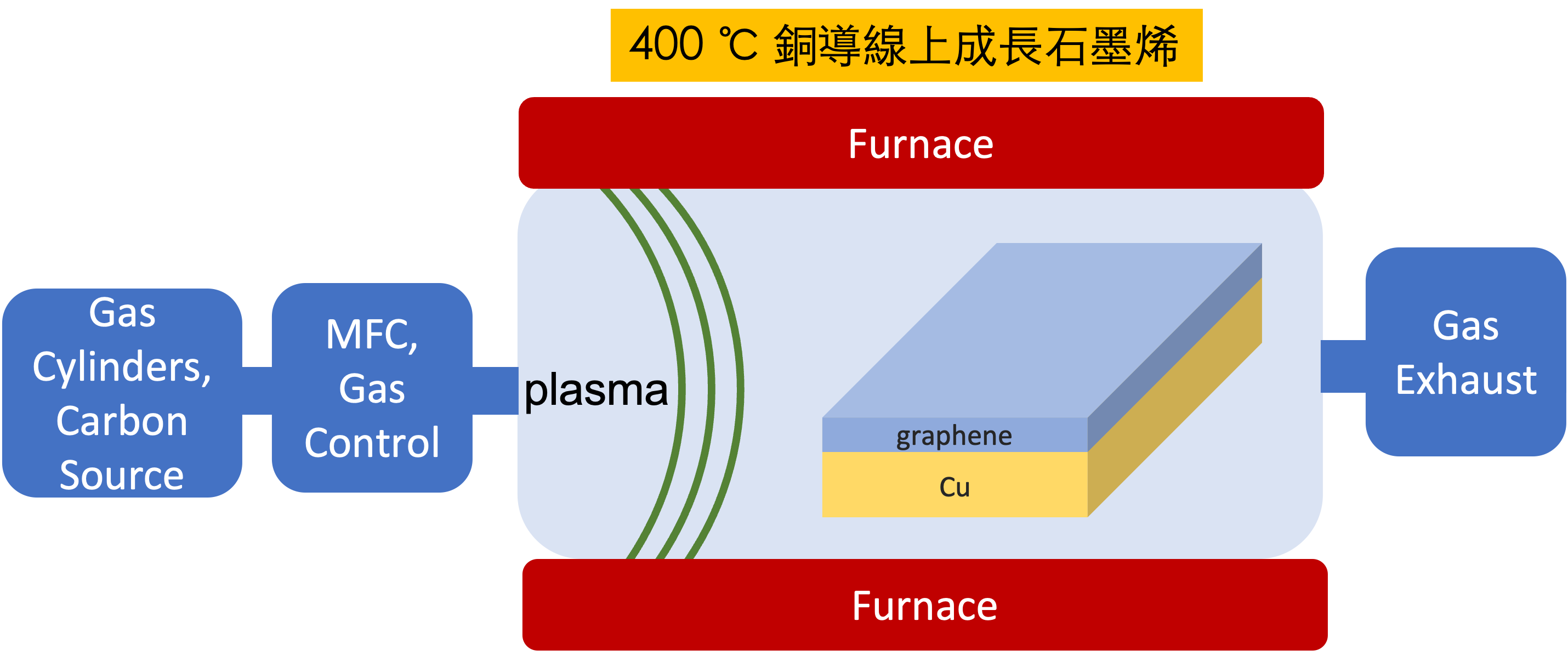

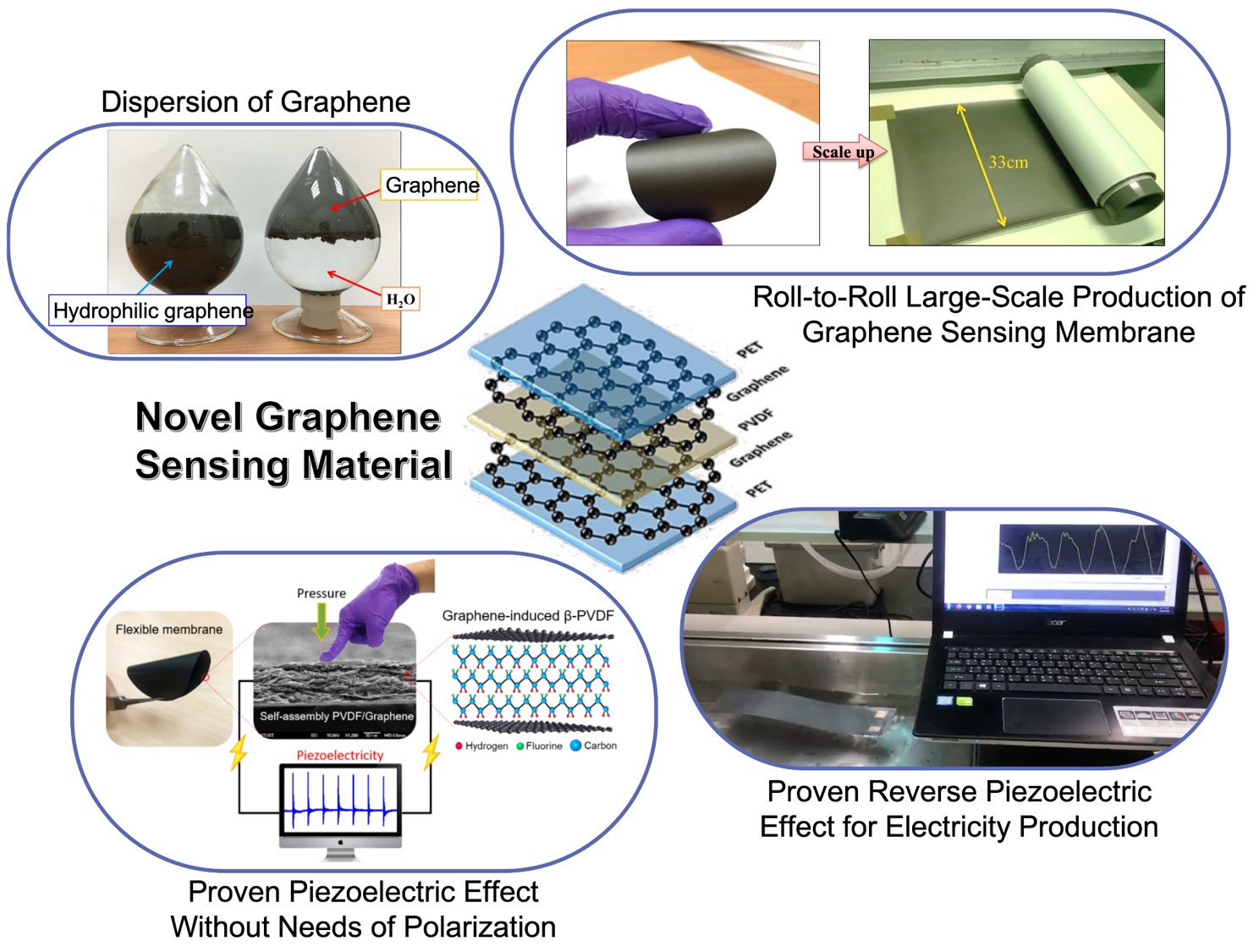

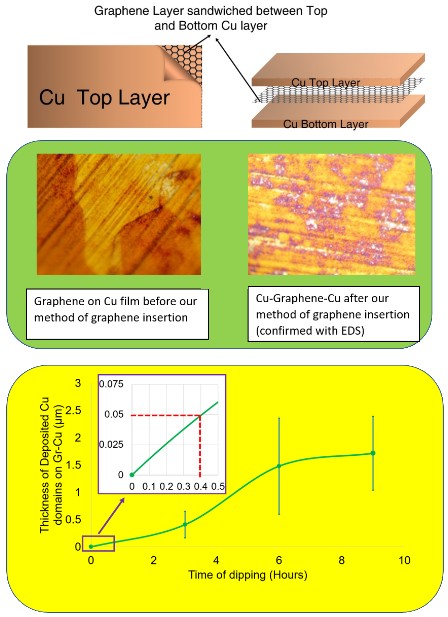

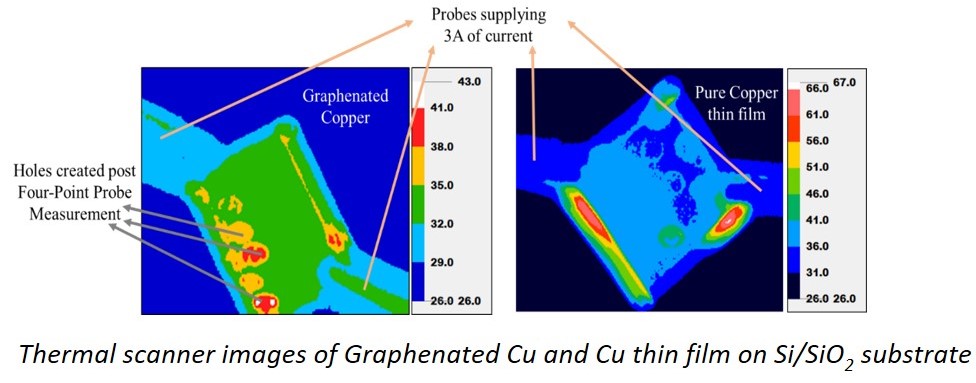

| 科學突破性 | 在VLSI互連線上進行低溫石墨烯沉積以實現後端工藝兼容性,以及將該石墨烯嵌入VLSI互連線內的方法,從而可以應用標準的成熟互連線工藝。 導電和導熱將通過嵌入的石墨烯進行,與任何金屬相比,石墨烯均具有出色的導電和導熱性,並且石墨烯的電遷移可靠壽命也比銅高出至少三倍。 |

||

| 產業應用性 | 本發明可用於所有互連線,包括集成電路以及印刷電路板。使用本發明的成本低,因為它僅需要硫酸銅溶液的浸沒槽。 |

||

| 關鍵字 | 互連線 超大規模集成電路 印刷電路板 銅 鋁 兼容晶片製造 可靠度 電遷移 電化學 石墨烯 | ||

- 聯絡人

- 林宜慧

- 電子信箱

- crest@mail.cgu.edu.tw

其他人也看了