| Technical Name | Implementation of hand gesture recognition with deep neural networkits hardware architecture design | ||

|---|---|---|---|

| Project Operator | National Central University | ||

| Project Host | 蔡宗漢 | ||

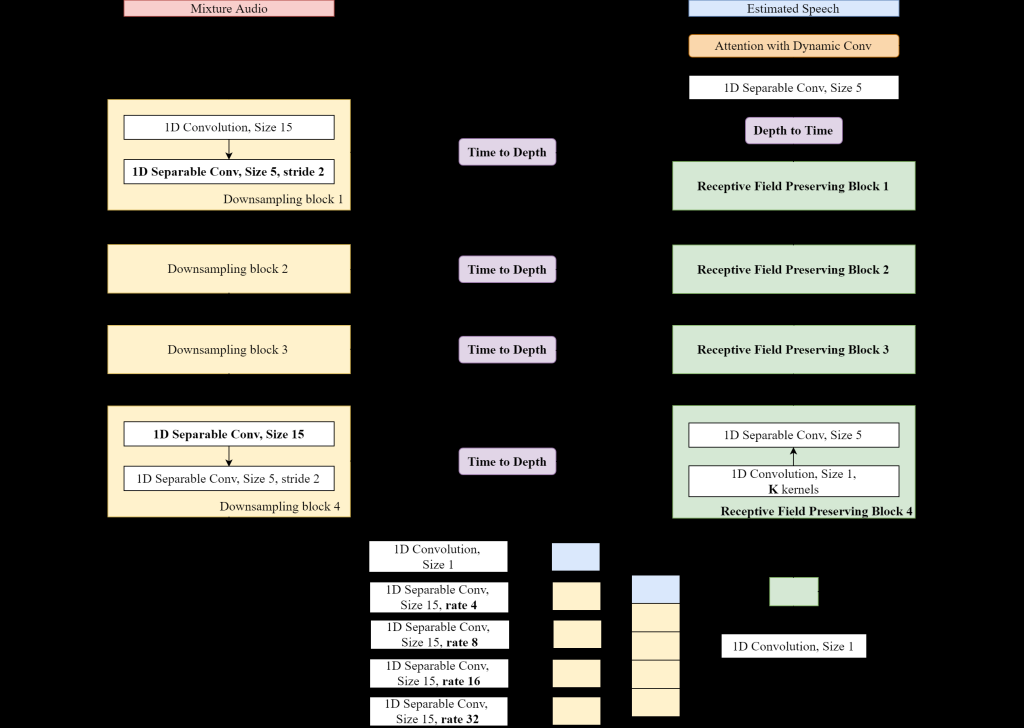

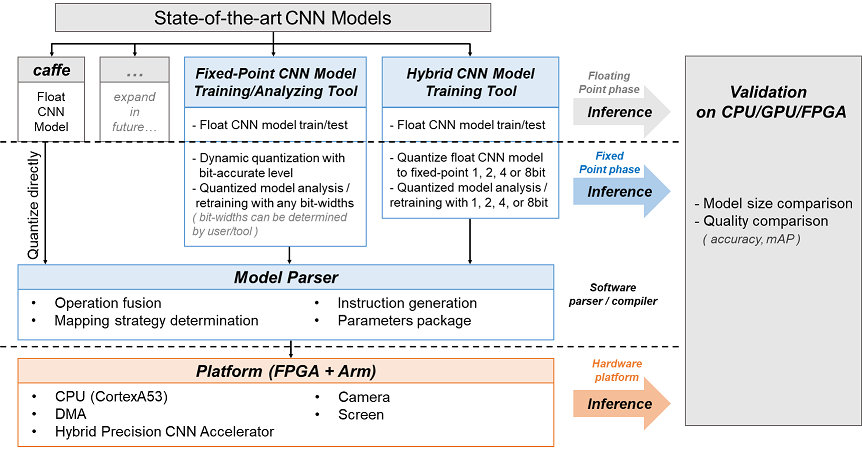

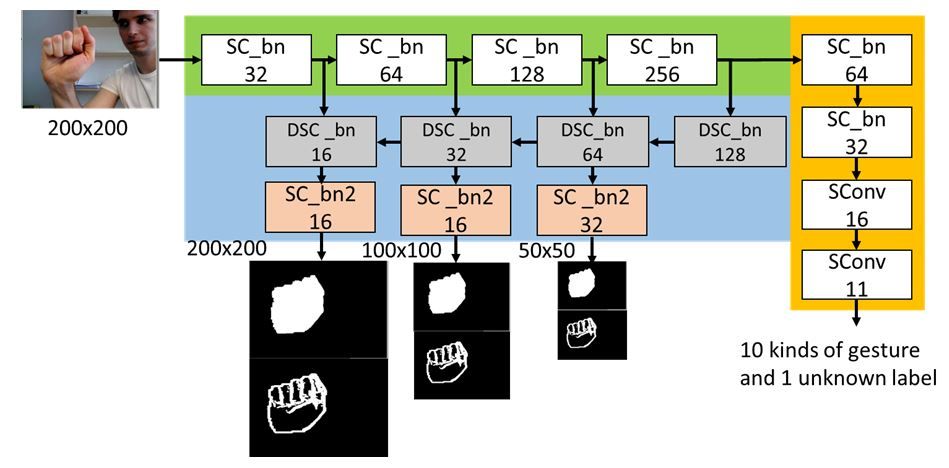

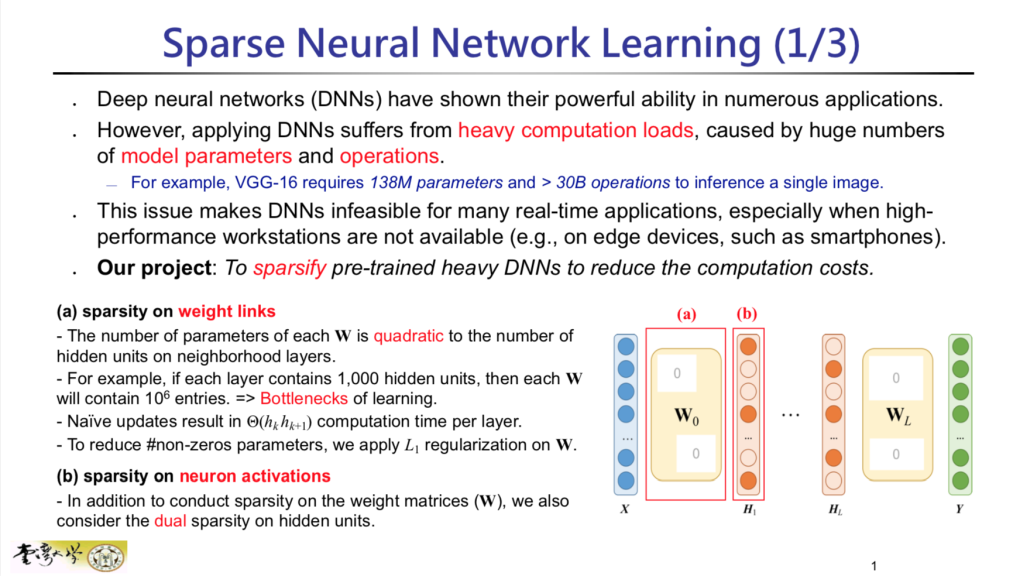

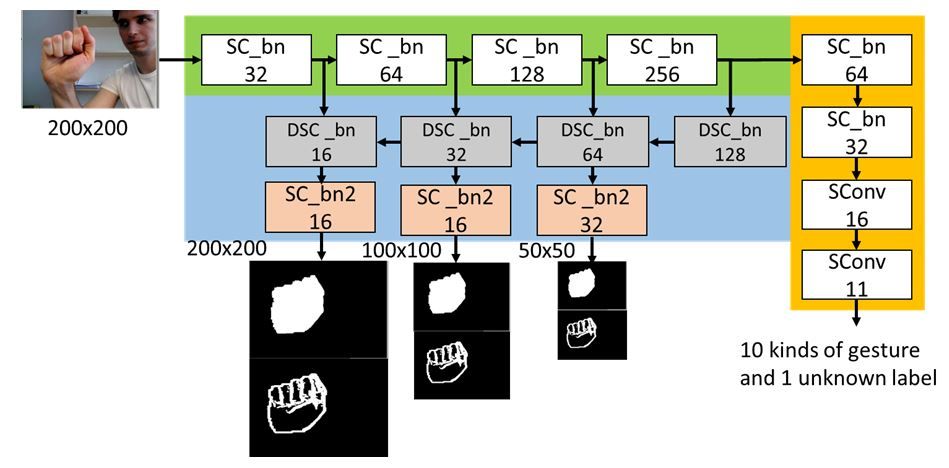

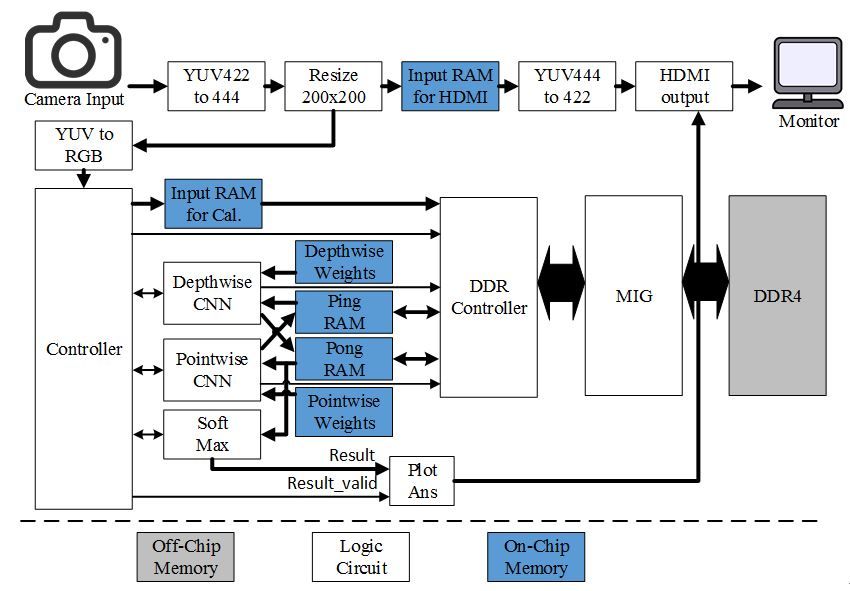

| Summary | This technology is a hardware implementation of hand segmentationrecognition system with deep neural network model. By using separable convolution layerattention module to both increase the execution speedevaluate performance. The implemented system can achieve the frame rate of 52.6fps65.6 GOPS. |

||

| Scientific Breakthrough | The gesture recognition of this design is tested in the OUHANDS data set. When the model size is 1.07MB, the recognition rate can reach 89.25. Implemented on the ZCU106 development board, the performance reaches 52.6FPS65.6 GOPS,the performance after quantifying on-chip memory is better than the existing depth separable convolutional hardware accelerator, which can reach 7.01 GOPS per M |

||

| Industrial Applicability | This technology uses a deep neural network to implement the hand gesture recognition method, which have a very good recognition rate in a complicated background using only a single CMOS camera. With the proposed neural network hardware accelerator, it is very suitable for use in the smart home appliances which can recognize gestures very quicklyprovide a more convenient operating environment |

||

| Keyword | Deep learning Deep neural network Convolutional neural network Depthwise separable convolution hand segmentation hand gesture recognition Attention model iteration training hardware accelerator FPGA | ||

- vivianchat11@yahoo.com.tw

other people also saw