| 技術名稱 | 高密度三維堆疊通孔電阻式記憶體 | ||

|---|---|---|---|

| 計畫單位 | 國立清華大學 | ||

| 計畫主持人 | 金雅琴 | ||

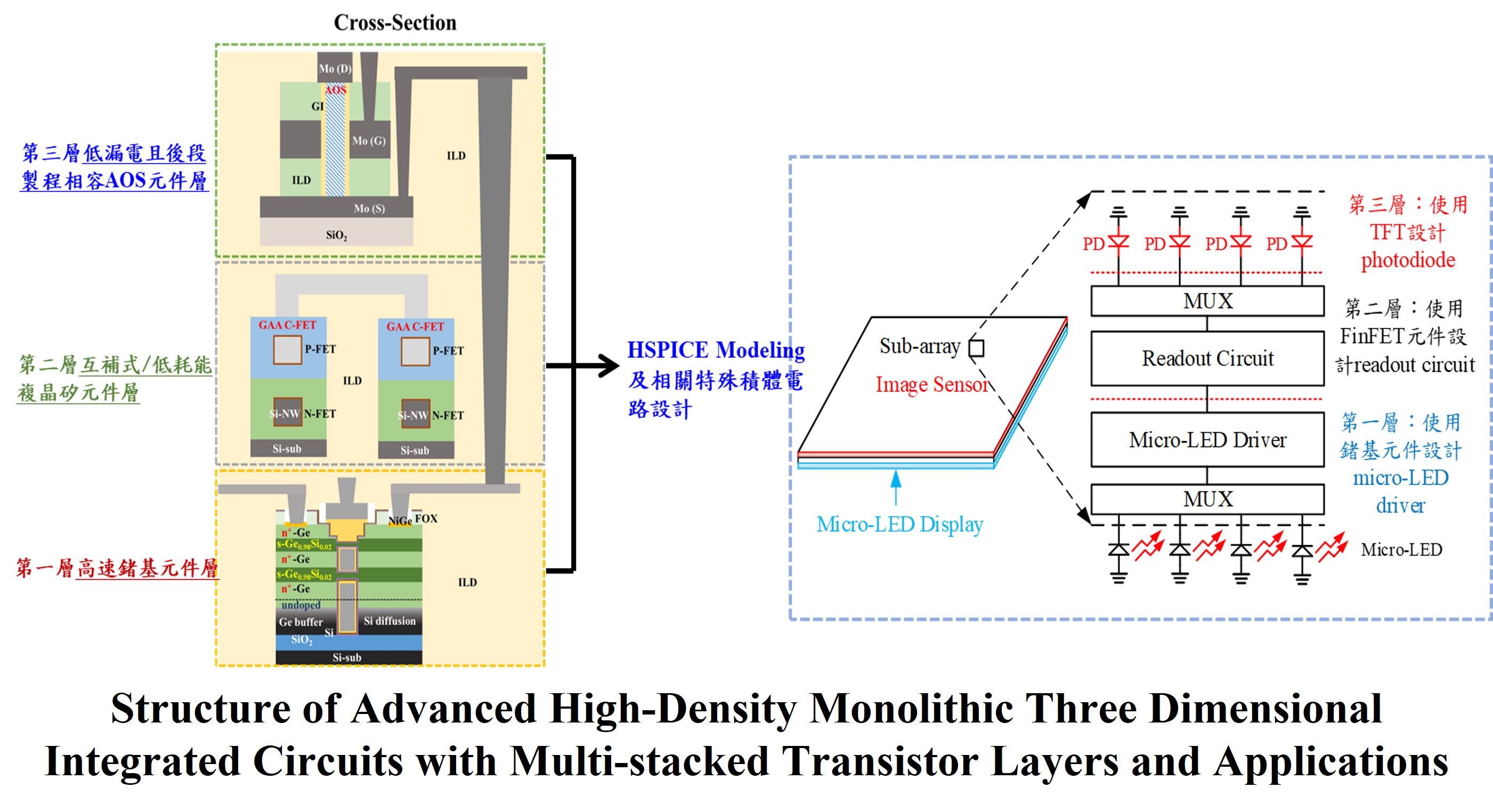

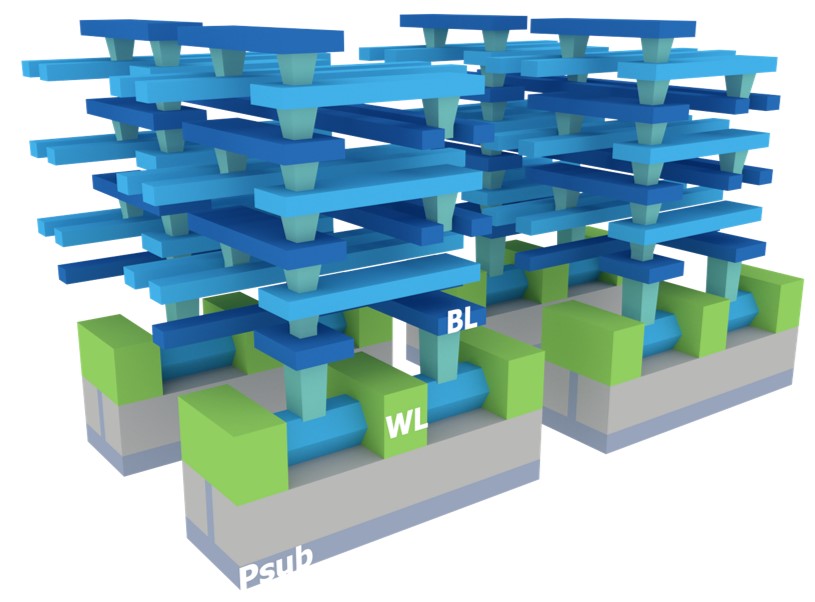

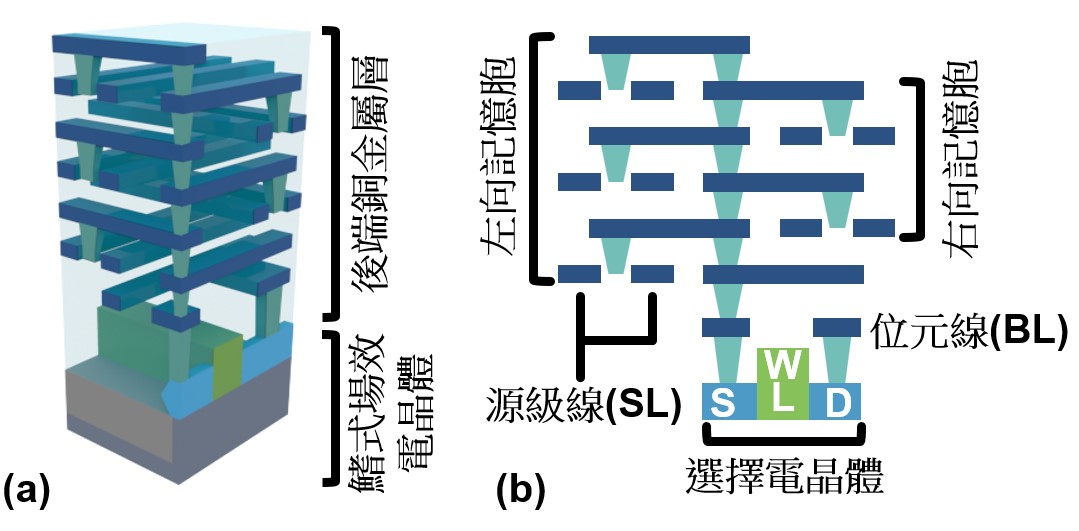

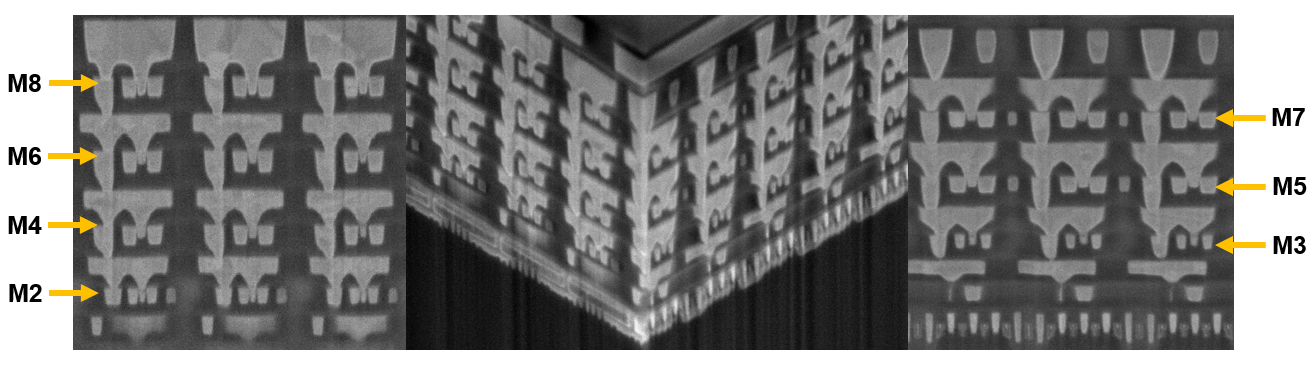

| 技術簡介 | 一種可相容於鰭式場效電晶體之CMOS邏輯製程的高密度三維通孔電阻式記憶體,透過在佈局中通孔與金屬導線層的不直接觸碰來形成通孔電阻式記憶體,並且透過可堆疊性,形成高密度的電阻式記憶體單元,進而完成高密度記憶體陣列。 |

||

| 科學突破性 | 由於「高密度三維通孔電阻式記憶體」可以内嵌入現有邏輯電路,因此它可以與現有技術相容,提供更多的可能性和彈性,從而滿足不同客戶的需求。此外,由於這種記憶體技術能夠在半導體尺寸不停微縮的技術節點上持續使用,它可以適應未來邏輯電路製程的演進,不會被淘汰,因此具有長期的應用前景。 |

||

| 產業應用性 | 「高密度三維通孔電阻式記憶體」透過領先業界的陣列特殊陣列方式,可大幅提升記憶體的儲存容量、資料讀取速度。利用現有標準半導體 FinFET 技術後端製程之金屬導線製作而成,可以完全相容且嵌入現有的高速運算晶片。在半導體尺寸微縮的技術節點上可持續使用,不會因跟不上邏輯電路日新月異製程的演進而被淘汰。 |

||

- 聯絡人

- 黃耀弘

- 電子信箱

- yhhuang.starlab@gapp.nthu.edu.tw

其他人也看了