| 技術名稱 | 具低功耗機制及多層式硬體安全性之微處理器系統 | ||

|---|---|---|---|

| 計畫單位 | 國立成功大學 | ||

| 計畫主持人 | 邱瀝毅 | ||

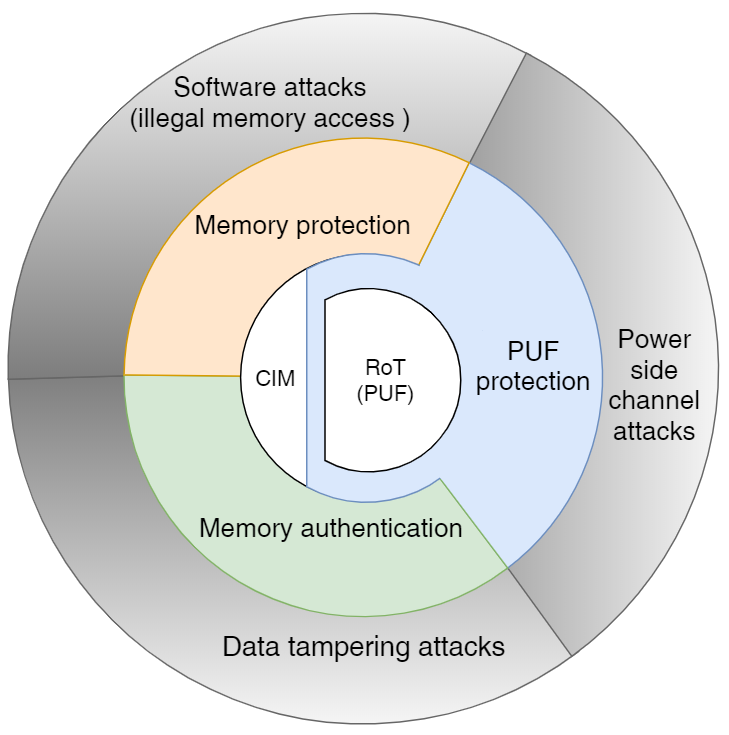

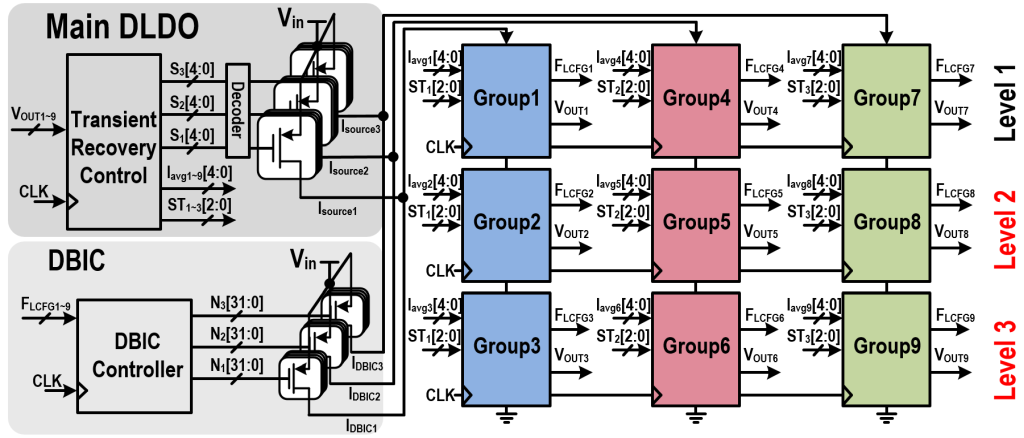

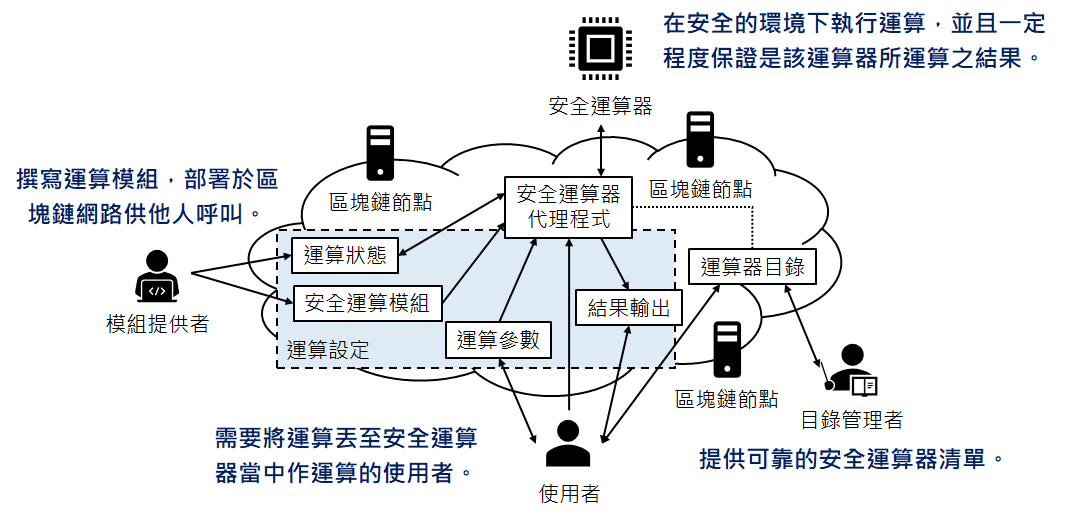

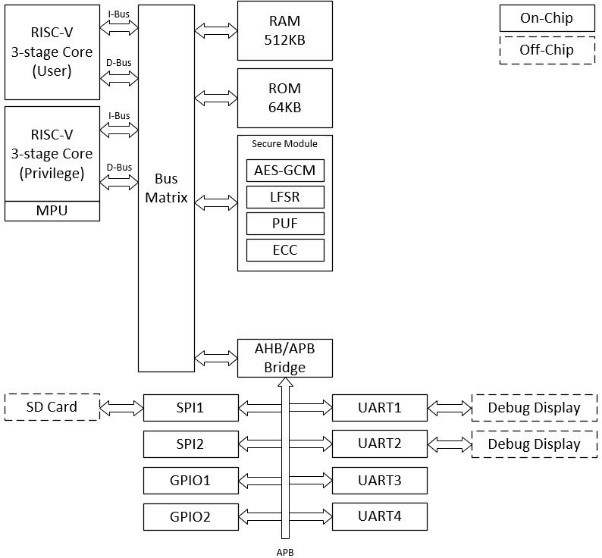

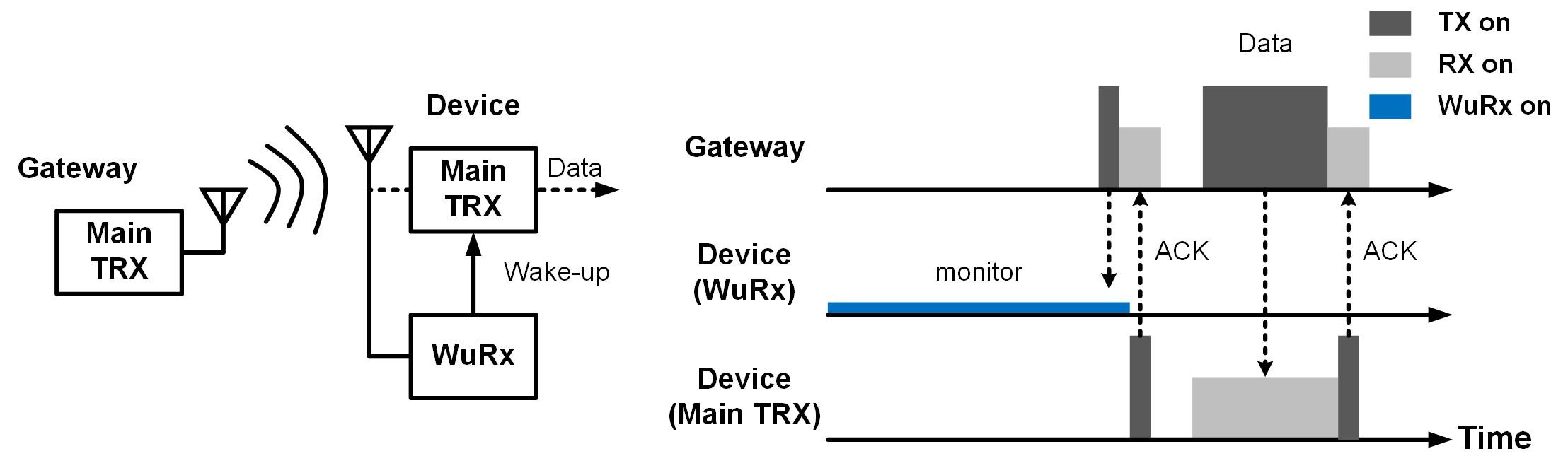

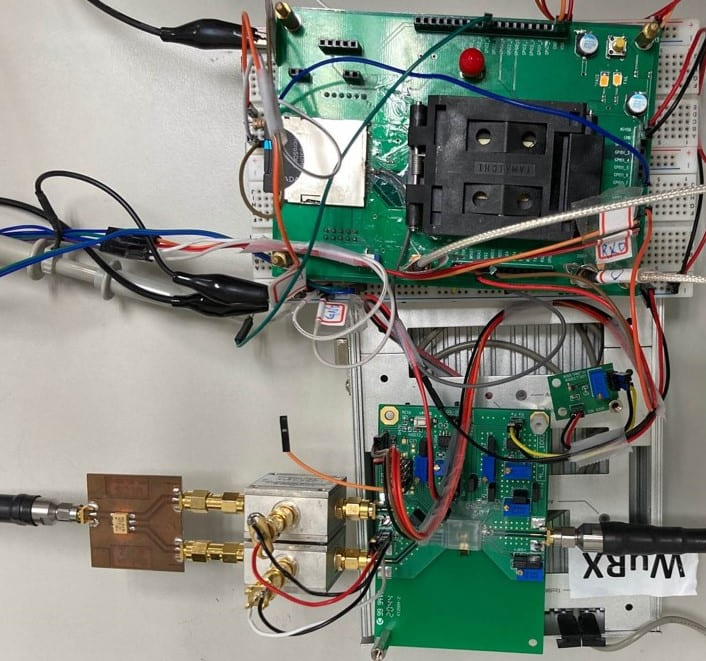

| 技術簡介 | 本安全處理器以物理密鑰作為信任根,發展出安全開機驗證流程、安全模組內更高安全性的加解密流程等,並可防止一般核心惡意存取、在安全核心植入惡意程式和旁側攻擊。此外,我們也使用記憶體保護機制保護機密資料。再透過整合具安全喚醒機制之無線收發機降低系統能源消耗及通訊延遲,實現低功耗與高安全性之系統。 |

||

| 科學突破性 | 本團隊自主開發之以物理密鑰作為信任根之硬體多層式安全微處理器晶片結合喚醒接收機,在確保系統硬體安全之同時也能達到低功耗要求,並且可以掌握智慧財產來源並增加系統更新權限與幅度。 |

||

| 產業應用性 | 本團隊能與現有物聯網與智慧穿戴醫療等應用相關產品有良好的整合性:在硬體安全上整合安全模組方便技術移植,並且多層式安全機制皆自主開發,可有效掌握系統更新權限。低功耗需求上支援多模的喚醒接收機、以及低運算量需求卻較嚴謹的身分驗證機制,可延長產品的電池壽命。期待本整合系統可以發展於更多項產業應用。 |

||

| 關鍵字 | 硬體安全 物理密鑰 安全開機驗證 加解密元件 旁路功擊保護 低功耗設計 無線感測網路 喚醒接收機 振幅/頻率/相位鍵控調變 一次性喚醒密碼 | ||

- 聯絡人

- 鄧士瑩

- 電子信箱

- teng0984229615@gmail.com

其他人也看了