| Technical Name | Ferroelectric Materials for the Acceleration of Artificial Intelligence Computation | ||

|---|---|---|---|

| Project Operator | National Cheng Kung University | ||

| Project Host | 盧達生 | ||

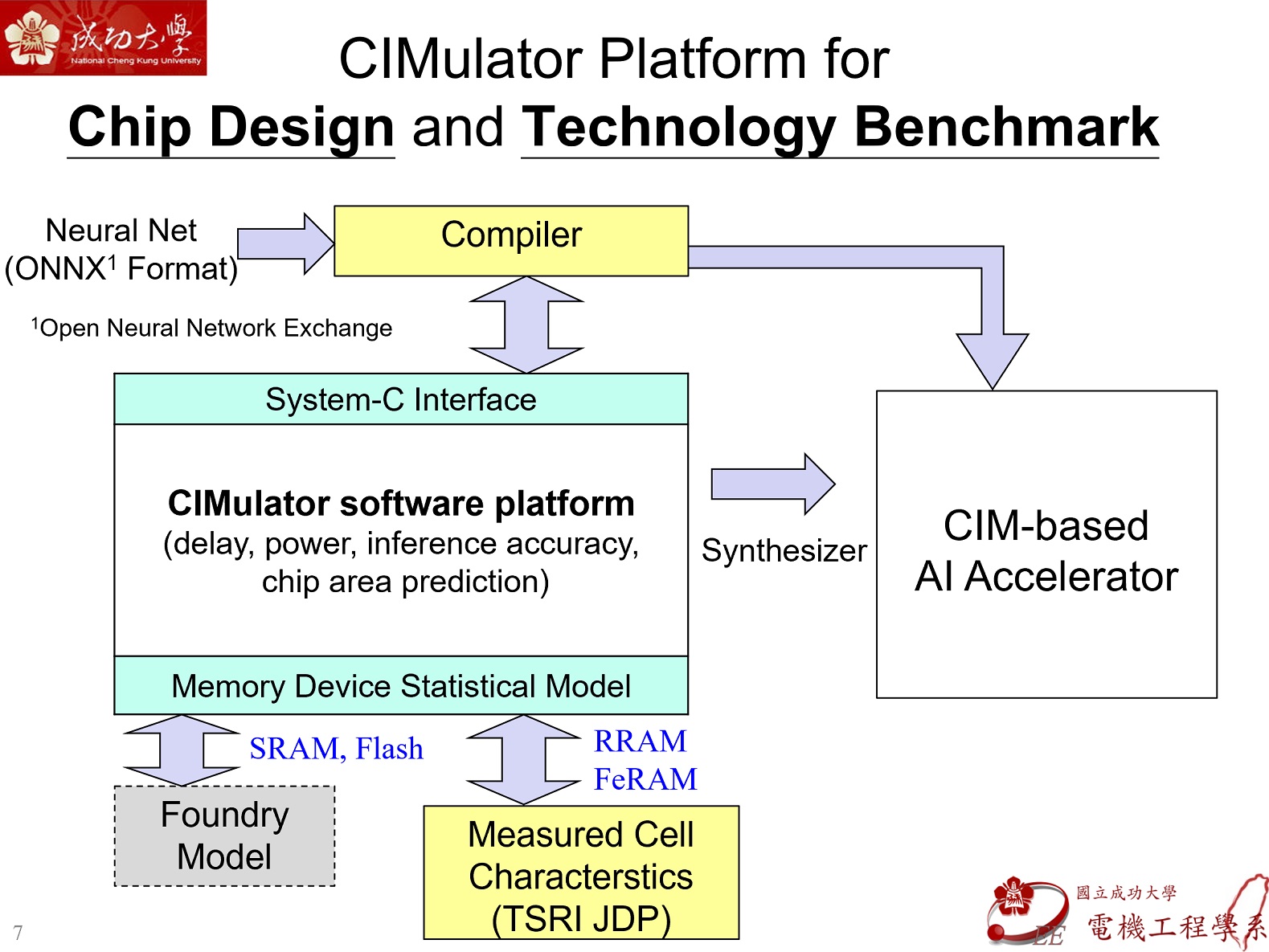

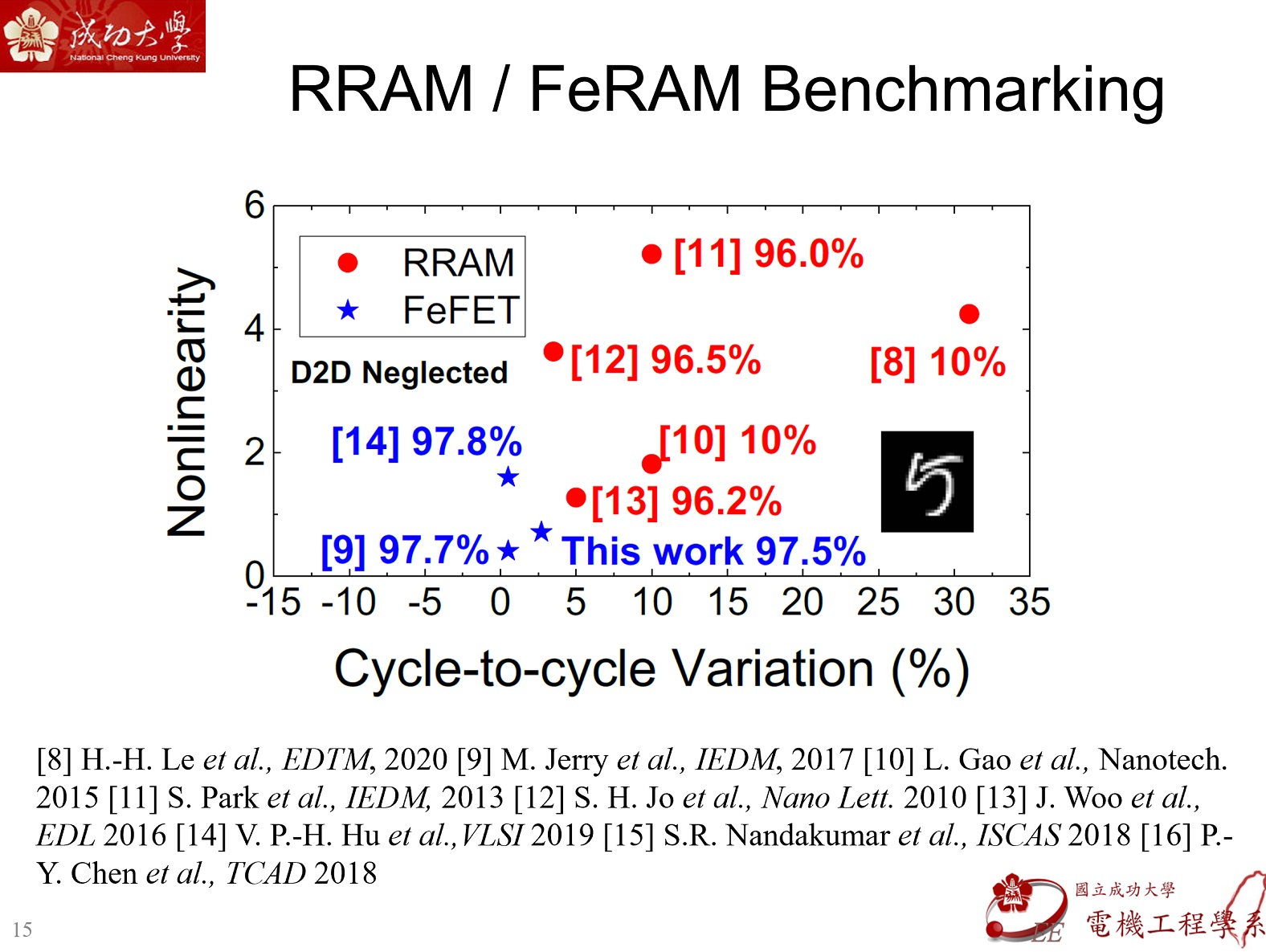

| Summary | With the ubiquity of artificial intelligence, dedicated chips to acceleration its computation is required. “Compute-in-memory” performs matrix vector multiplications using a memory array in an analog manner, enabling large throughput, high power and area efficiency. Memory devices based on ferroelectric material have both small area and good endurance, which makes it a promising candidate technology. |

||

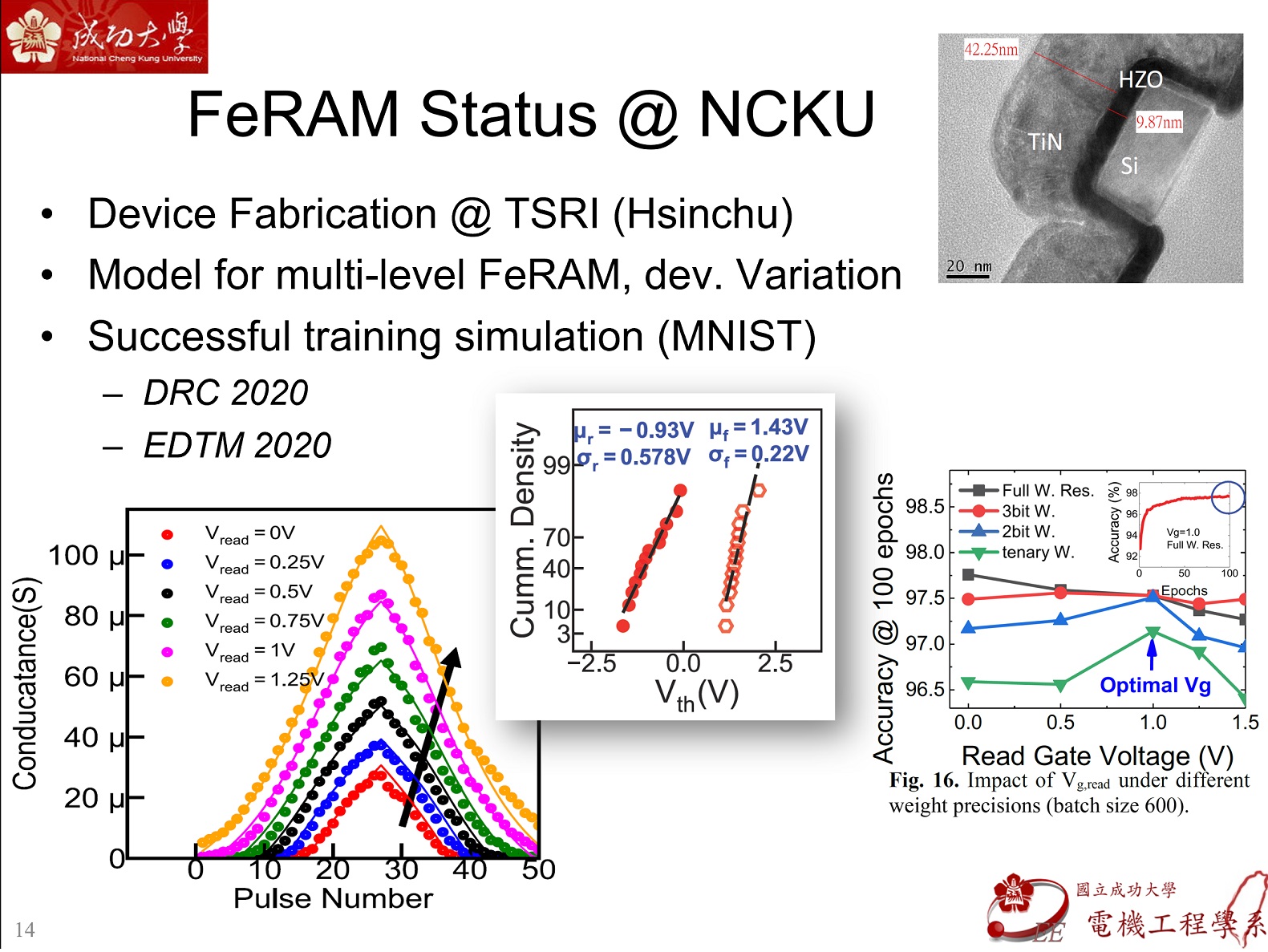

| Scientific Breakthrough | Conventional Lead-Zirconium-Titanite ferroelectric memory may cause contamination in a semiconductor process, therefore it is difficult to integrate with standard CMOS beyond 130nm. Around 2007, hafnium-zirconium-oxide was discovered as new ferroelectric material. We have successfully fabricated HZO ferroelectric memory transistors at Taiwan Semiconductor Research Institute. Key technologies developed are: |

||

| Industrial Applicability | 1.Semiconductor fabrication companies may use our technology to introduce new materials, and improve the effectiveness of memory products |

||

| Keyword | Ferroelectric material Transistor Artificial neural networks Artificial intelligence Deep learning Semiconductor processing Circuit design Computing in memory | ||

- darsenlu@mail.ncku.edu.tw

other people also saw